Le fournisseur américain de cartes et plateformes pour applications critiques miltaires et aérospatiales Mercury Systems propose avec la carte au format 3U OpenVPX référencée Model 5560 une solution en châssis de cotraitement de données fondée sur l’utilisation de la puce programmable Versal HBM d’AMD Xilinx, initialement conçue pour le marché des centres de données.

Les puces Versal HBM (High Bandwidth Memory) intègrent une mémoire DRam HBM2E directement sur le circuit intégré, l’ensemble offrant un débit de 820 Go/s et une capacité de 16 Go pour une bande passante mémoire 8 fois supérieure à celle des mémoires externes DDR5 et une consommation d'énergie 63% inférieure.

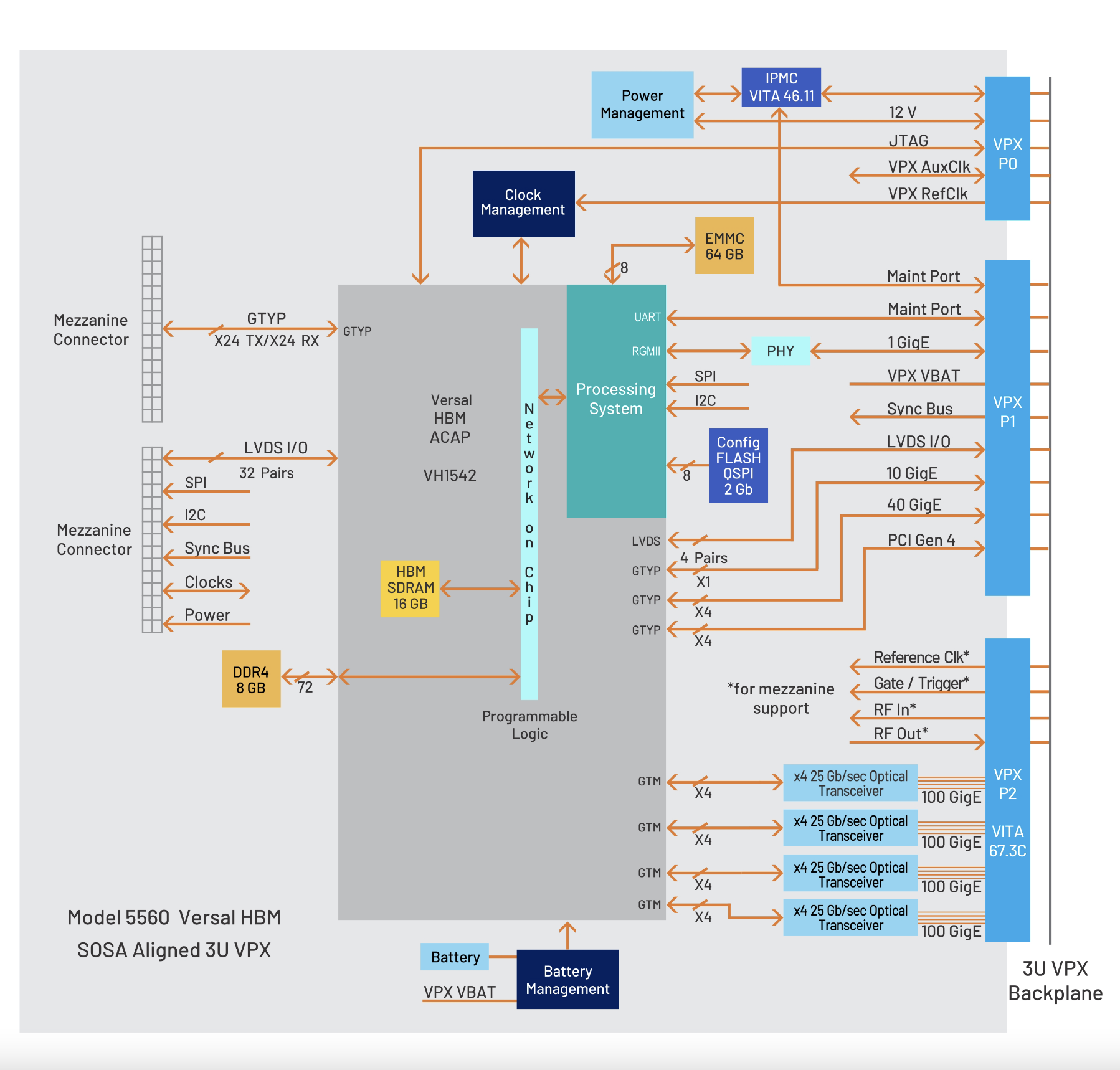

La puce Versal HBM, gravée en 7 nm et modifiable aussi bien au niveau logiciel que matériel, s’appuie sur l’architecture ACAP (Adaptive Compute Acceleration Platform) d’AMD Xilinx où cohabitent sur le circuit une matrice FPGA, des blocs DSP programmables et un SoC multicœur, reliés entre eux par un réseau-sur-puce (NOC, Network-On-Chip).

Selon Mercury, ce type d’architecture répond aux besoins des applications de guerre électronique et de traitement spectral utilisées par les plates-formes terrestres, aériennes et maritimes qui doivent capturer des signaux en entrée, les traiter et fournir des signaux de sortie exploitables dans des délais extrêmement courts.

Toujours selon Mercury, de nombreux systèmes de Défense existants utilisent déjà des FPGA comme coprocesseurs pour accélérer le traitement des données mais ils se heurtent à des goulots d'étranglement lorsque les données sont transférées vers une mémoire positionnée ailleurs sur la carte.

Dans le détail, la carte OpenVPX Model 5560 de Mercury intègre en sus 8 Go de mémoire SDRam DDR4 haut débit, quatre canaux de données optiques à haut débit de 100 Gigabit Ethernet pour un débit de données agrégé de 50 Go/s.

Pou rappel, Mercury a déjà intégré des FPGA Versal sur ses cartes, en l'occurrence les modèles Versal AI, sur une carte 6U OpenVPX (voir notre article)

Un kit de conception pour le FPGA - FPGA Navigator - et un ensemble de BSP sont fournis pour faciliter le contrôle opérationnel de la plate-forme et le développement de blocs d’IP.