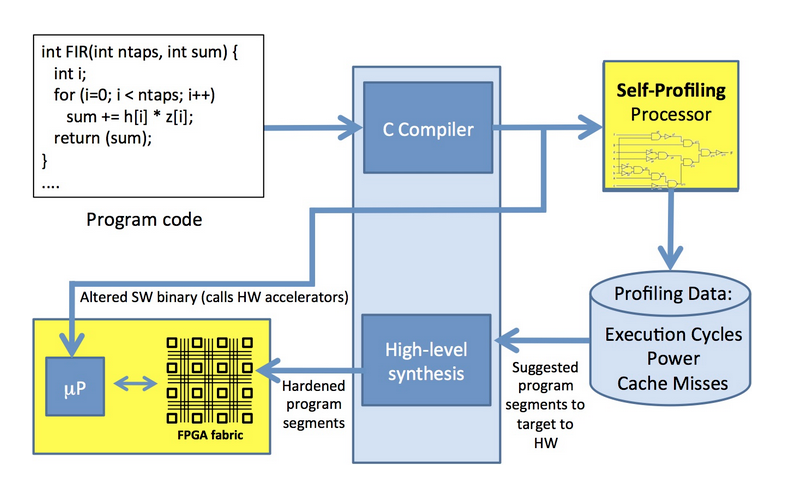

Microchip Technology annonce ce jour l'acquisition pour un montant non dévoilé de la jeune société canadienne LegUp Computing, fondée en 2015, basée à Toronto et éditrice de l’environnement de synthèse de haut niveau (HLS, High Level Synthesis) pour FPGA LegUp HLS.... Objectif affiché par Microchip pour ce rachat : simplifier le processus de développement des solutions logicielles de calcul à bord des FPGA PolarFire de la société, en autorisant le “mappage” direct d’applications écrites en C/C++ sur le FPGA.

Issu des travaux de recherche de l’université de Toronto, l’outil LegUp HLS ouvre la programmation des plates-formes PolarFire (FPGA et SoC) à une plus grande communauté d’ingénieurs logiciels dans le but d’exploiter plus facilement la puissance d’accélération disponible sur ces architectures.

« L'équipe de LegUp nous apporte une expérience approfondie de la synthèse de haut niveau et des technologies associées, alors que nous continuons d'optimiser en parallèle les flux d'outils de conception intégrés pour les utilisateurs des architectures PolarFire, commente Bruce Weyer, vice-président de l'unité commerciale FPGA chez Microchip. Cette acquisition donne également la possibilité aux utilisateurs de nos processeurs et microcontrôleurs d’utiliser des FPGA comme accélérateurs grâce à un compilateur facile à utiliser qui améliore la productivité des designs. »

L'outil LegUp HLS sera utilisé avec le kit de conception de logiciels VectorBlox Accelerator et le générateur d'IP de réseaux de neurones CoreVectorBlox de Microchip pour fournir une pile complète aux développeurs d'algorithmes écrits en C/C ++ qui souhaitent travailler avec les PolarFire sans avoir à comprendre les subtilités des flux de développement au niveau registre (RTL), habituellement maîtrisées par les développeurs de solutions sur FPGA. Rappelons que Microchip a acquis la société VectorBlox Computing, sise à Vancouver au Canada, en août 2019, afin d'améliorer son portefeuille de solutions pour les applications de calcul en périphérie de réseau (Edge Computing).

L'outil LegUp HLS sera utilisé avec le kit de conception de logiciels VectorBlox Accelerator et le générateur d'IP de réseaux de neurones CoreVectorBlox de Microchip pour fournir une pile complète aux développeurs d'algorithmes écrits en C/C ++ qui souhaitent travailler avec les PolarFire sans avoir à comprendre les subtilités des flux de développement au niveau registre (RTL), habituellement maîtrisées par les développeurs de solutions sur FPGA. Rappelons que Microchip a acquis la société VectorBlox Computing, sise à Vancouver au Canada, en août 2019, afin d'améliorer son portefeuille de solutions pour les applications de calcul en périphérie de réseau (Edge Computing).

« Les ingénieurs logiciels ont besoin d'une accélération matérielle pour atteindre les performances attendues dans une enveloppe énergétique maîtrisée, et ils recherchent des outils qui permettent de travailler à des niveaux d'abstraction élevés pour programmer directement le matériel, précise Andrew Canis, PDG de LegUp Computing. Au sein de Microchip, nous allons contribuer à alimenter l’innovation pour les applications de type edge computing, en permettant aux développeurs de tirer parti d'algorithmes logiciels développés en C/C ++ portés par la suite vers des architectures à faible consommation, comme les FPGA et SoC PolarFire. »

Microchip va mettre l'outil LegUp HLS à la disposition d’utilisateurs avancés dès maintenant et déploiera un flux de conception intégré complet au cours du premier semestre 2021.

Pour rappel, les outils de synthèse de haut niveau, dits HLS, sont apparus sur le marché à la fin des années 90, popularisés notamment par l’outil Catapult lancé en 2004 par Mentor Graphics. Ces solutions, qui ont eu un succès commercial mitigé, sont des outils qui captent en entrée du code C ou C++ non “timé” (sans signal d’horloge) et qui génèrent un code RTL (Register Transfer Level) optimisé pour une synthèse sur les structures matérielles d’un FPGA. Un des avantages de cette approche vient du fait que les modèles développés en C++ sont vérifiés beaucoup plus rapidement et avec des coûts bien moindres que du code RTL.

Chez Intel (qui a investi dans le capital de LegUp en janvier 2018), on trouve un outil similaire, Intel HLS, issu d’Altera qui est intégré au sein de la suite de développement Quartus. Chez Xilinx, de manière identique, on trouve l’outil Vivado HLS intégré dans l’environnement pour FPGA Vivado.

-dissolve-basic-fr.jpg)