Afin de faciliter la création de solutions de vision embarquée intelligentes fondées sur des FPGA basse consommation, Microchip lance un SDK (Software Development Kit) baptisé VectorBlox Accelerator et un bloc d’IP de réseau de neurones ad hoc. ...L'offre est censée procurer aux développeurs logiciels une voie simple pour programmer et implanter un réseau de neurones préentrainé sur un circuit programmable sans qu'ils soient des experts de ce type d’architecture.

Avec l'essor de l'intelligence artificielle, de l'apprentissage automatique et de l’Internet des objets, certaines applications migrent vers la périphérie de réseau (edge), là où les données sont collectées, rappelle Microchip. Ce qui réclame des solutions à faible consommation capables de fournir des performances de calcul en hausse dans des environnements sécurisés et contraints en termes d’espace physique. D’où l’initiative Smart Embedded Vision lancée en juillet 2019 par la société de semi-conducteurs qui répond à ces besoins en permettant aux développeurs logiciels de mettre en œuvre plus facilement leurs algorithmes sur des FPGA, en particulier sur le PolarFire de la société.

Dans ce cadre général, le kit de développement logiciel VectorBlox Accelerator de Microchip permet aux développeurs de tirer parti des caractéristiques intrinsèques du PolarFire pour créer des applications basse consommation, sans être des experts des FPGA. Ce type d’architecture est théoriquement capable d’effectuer davantage d'opérations par seconde avec un meilleur rendement énergétique qu'un processeur classique de type CPU ou GPU, assure Microchip.

Dans ce cadre général, le kit de développement logiciel VectorBlox Accelerator de Microchip permet aux développeurs de tirer parti des caractéristiques intrinsèques du PolarFire pour créer des applications basse consommation, sans être des experts des FPGA. Ce type d’architecture est théoriquement capable d’effectuer davantage d'opérations par seconde avec un meilleur rendement énergétique qu'un processeur classique de type CPU ou GPU, assure Microchip.

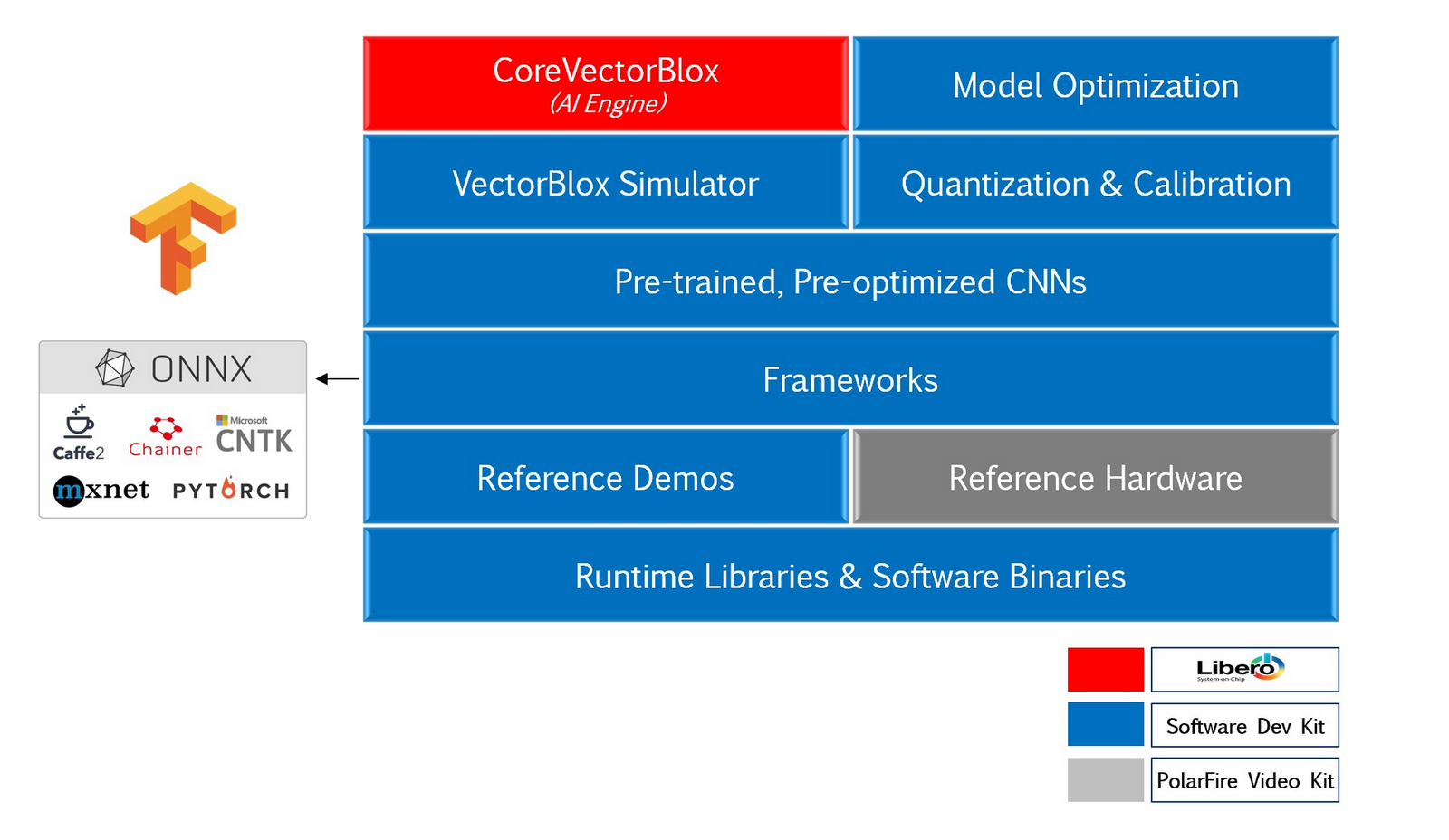

Mais en revanche ils nécessitent des compétences matérielles spécifiques. C’est pourquoi le SDK VectorBlox Accelerator, qui fonctionne sous Linux et Windows, permet aux développeurs de coder en C/C++ et de programmer des réseaux de neurones sans expérience préalable de conception en FPGA. Il intègre également un simulateur précis au bit près, permettant à l'utilisateur de valider la précision du matériel dans son environnement logiciel. L’IP de réseau de neurones inclus dans le kit permet quant à elle de charger différents modèles de réseau en cours d'exécution.

In fine VectorBlox Accelerator et l’IP de réseau de neurones apportent aux développeurs logiciels et matériels un moyen de mettre en œuvre une architecture à réseau de neurones convolutif, avec une gestion d’overlay souple sur les FPGA PolarFire.

Le kit d'outils sait faire tourner des modèles au format TensorFlow ou au format ONNX (Open Neural Network Exchange), ce dernier offrant une interopérabilité assez large entre applications, via la compatibilité de nombreux environnements de développement capables de programmer des réseaux de neurones comme Caffe2, MXNet, PyTorch et Matlab.

Pour mémoire, côté consommation, les FPGA PolarFire permettent une réduction de consommation de 50% par rapport aux circuits concurrents, tout en offrant une puissance de calcul supérieure de 25%, pouvant atteindre 1,5 Tops (téraopérations par seconde), selon les chiffres avancés par Microchip. Ces circuits adaptés à des applications de type caméra intelligente peuvent intégrer sur la même puce l'ensemble du pipeline du traitement du signal d'image, c’est-à-dire l'interface du capteur, le contrôleur mémoire DDR, l'IP de traitement d'image et les interfaces réseau, en plus du moteur d’inférence d'apprentissage automatique.

Le SDK VectorBlox Accelerator devrait être disponible au cours du troisième trimestre 2020, après la mise en place d'un programme de type Early Access en juin.

-dissolve-basic-fr.jpg)