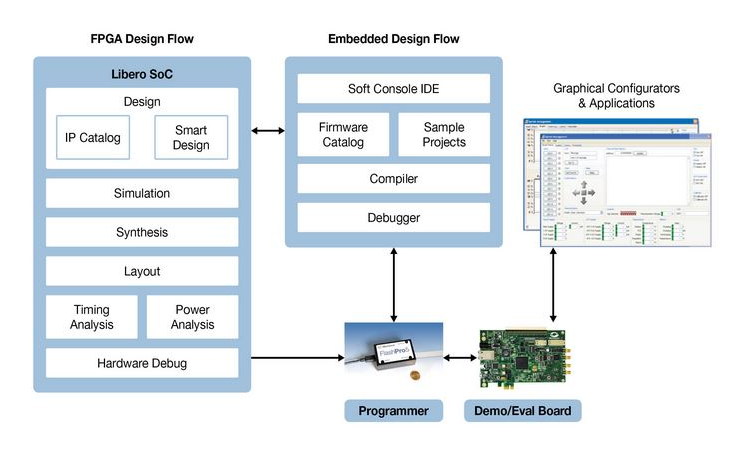

Les conceptions sur les architectures de type FPGA (Field Programmable Gate Array) sont de plus en plus complexes et nécessitent d’avoir à disposition des outils de conception à la hauteur en termes de productivité. ...Avec la version 12.0 de son environnement Libero SoC, Microchip, via sa filiale Microsemi, estime, dans ce cadre, offrir des gains en termes de temps d'exécution et de qualité des résultats, ainsi qu'une suite de conception unifiée pour toutes les solutions de dernière génération de l'entreprise, y compris les FPGA de la gamme PolarFire.

Selon Microchip, en passant à la version 12.0 de Libero SoC, les concepteurs obtiennent des réductions de 60% du temps d'exécution (pour la partie timing), de 25% de la surface sur silicium via l’optimisation des fonctions de placement-routage, et de 18% pour la consommation. Avec en outre une augmentation moyenne de 4% de la qualité des résultats pour les conceptions de grande taille et une amélioration notable de 10% pour les architectures PolarFire MPF300 / TS-1.

Libero SoC 12.0 est publié simultanément pour les versions MPF100T, MPF200T et MPF300T des FPGA PolarFire avec la prise en charge sur ces architectures des points d’arrêt matériels (FHB, FPGA Hardware Breakpoint) pour le débogage. La version de cet environnement intègre aussi la programmation de l’architecture des timings (structure temporelle des signaux à bord) et la gestion de la consommation (signaux d’alimentation) des FPGA destinés aux secteurs de l'aérospatiale et de la Défense, comme les RT4G150L, tolérants aux radiations. Elle est aussi compatible avec les SmartFusion2 (version M2S150T S) utilisés dans les applications militaires.

Enfin signalons que la fonction SmartDebug permet désormais de surveiller les blocs émetteurs-récepteurs insérés au sein des FPGA. Cette suite de conception unifiée pour les FPGA des gammes PolarFire, Igloo2, SmartFusion2 et RTG4 élimine ainsi de fait, selon Microchip, le besoin pour les concepteurs de qualifier plusieurs logiciels pour leurs projets.