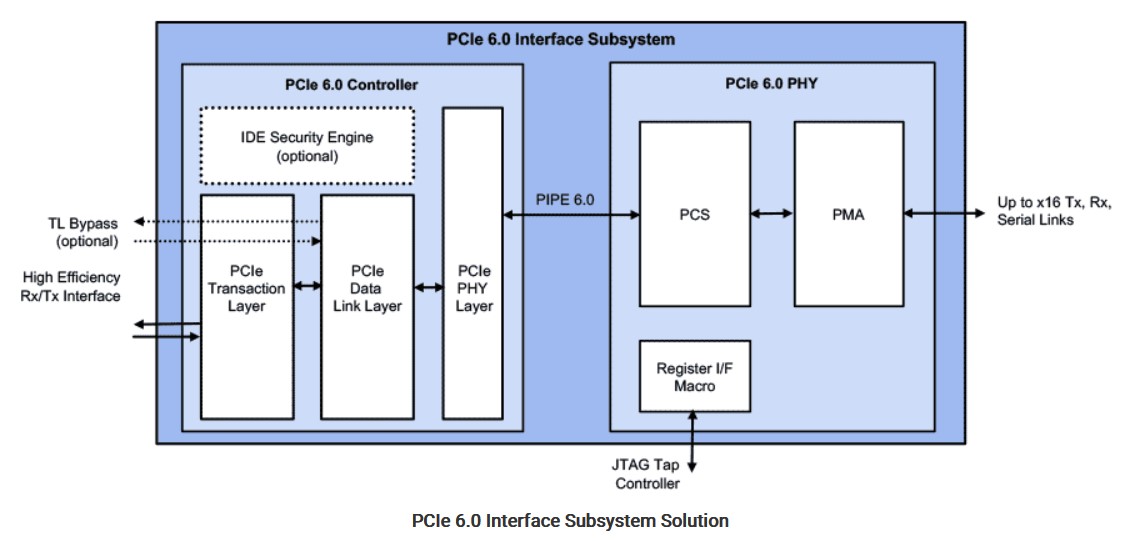

La société Rambus, qui commercialise des blocs d’IP et des puces d’accélération et de sécurisation des données, annonce la disponibilité d’un sous-système d'interface PCI Express 6.0 composé d’une IP de couche physique (PHY) et d’une IP de contrôle. Le bloc PHY PCIe 6.0 de Rambus est également compatible avec la dernière version en date de la spécification Compute Express Link (CXL), la version 3.0.

Pour rappel, la spécification PCIe 6.0, publiée début 2022, porte la vitesse du vénérable bus d’entrées/sorties à 64 gigatransferts par seconde (GT/s) par lien unidirectionnel (grâce notamment à la mise en œuvre de la modulation PAM-4), contre 32 GT/s pour le PCIe 5.0, tout en maintenant des caractéristiques de basse consommation et la rétrocompatibilité avec les générations précédentes. Ce qui devrait permettre de transférer un débit maximal de 256 Go/s dans une configuration à 16 liens (x16).

Le standard PCIe 6.0 est considéré comme essentiel aux concepteurs de puces-systèmes SoC et aux architectes système qui développent les circuits intégrés de nouvelle génération aptes à transférer des flux massifs de données au sein d’équipements divers et variés dans les domaines comme les centres de données, le calcul à hautes performances (HPC), l’intelligence artificielle et l’apprentissage automatique, l’Internet des objets haut de gamme, la Défense, l’aérospatial et l’automobile.

Le sous-système d'interface Rambus PCIe 6.0, qui assure des débits de données allant jusqu'à 64 GT/s, a été entièrement optimisé pour répondre aux besoins des architectures de traitement hétérogènes avancées. Au sein du sous-système, le contrôleur PCIe dispose d'un moteur d'intégrité et de chiffrement des données (IDE) dévolu à la protection des liaisons PCIe et des données qui y sont transférées. Du côté PHY, la prise en charge complète de CXL 3.0 vise à permettre la mise en œuvre au niveau puce de mécanismes de partage, d'extension et de mise en commun de la mémoire avec cohérence de cache.

Parmi les autres caractéristiques du sous-système d’interface PCIe 6.0 de Rambus, on citera la rétrocompatibilité avec les spécifications PCIe 5.0, 4.0 et 3.0/3.1, un codage FEC (Forward Error Correction) à faible latence pour assurer la robustesse des liaisons, et la prise en charge de la structure fixe de paquets pour l’échange de données Flit (Flow Control Unit), destinée à assurer une meilleure efficacité dans l’utilisation de la bande passante.

On rappellera que Rambus a racheté en 2021 la société française PLDA, spécialiste des blocs d’IP d’interconnexion PCI Express et CXL.

-dissolve-basic-fr.jpg)