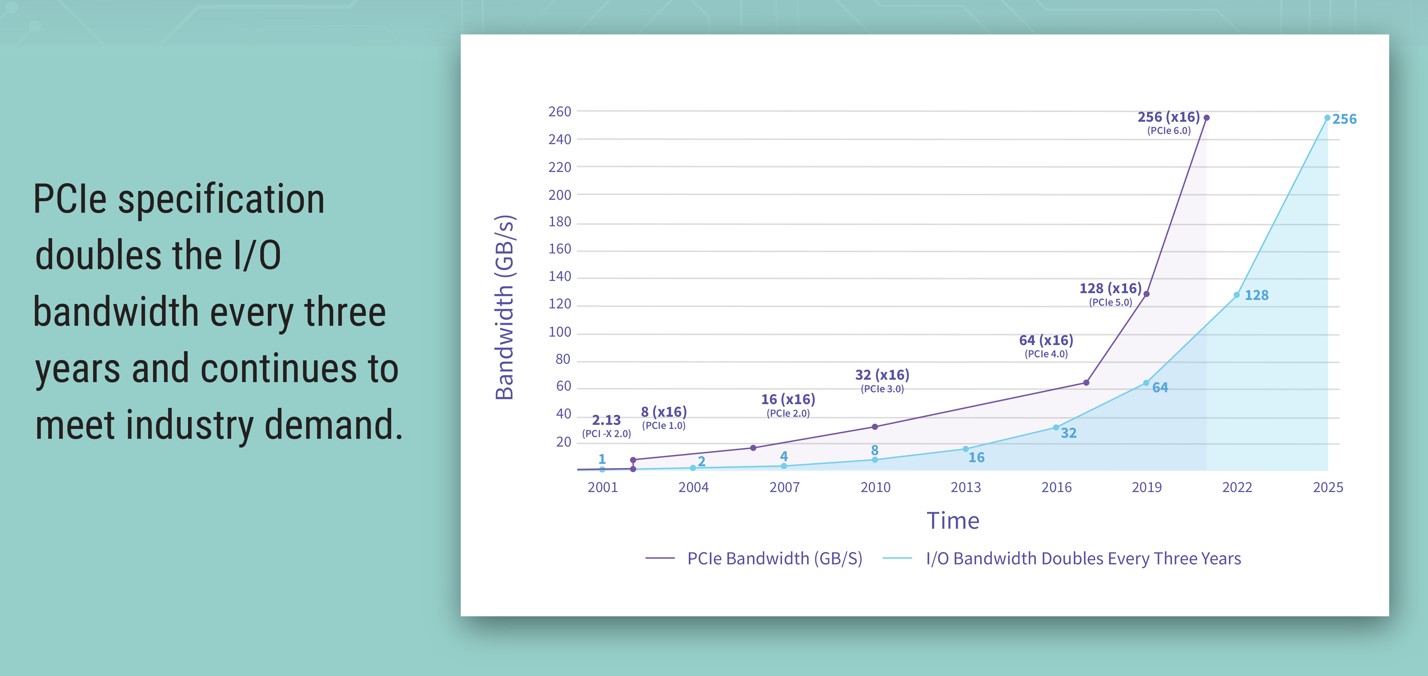

L’organisme PCI-SIG, qui préside aux destinées du standard PCI Express, a annoncé hier 11 janvier 2022 la publication officielle de la spécification PCIe 6.0. Celle-ci porte la vitesse du vénérable bus d’entrées/sorties à 64 gigatransferts par seconde (GT/s) par lien unidirectionnel, contre 32 GT/s pour le PCIe 5.0 ratifié il y a trois ans, tout en maintenant des caractéristiques de basse consommation et la rétrocompatibilité avec les générations précédentes. Ce qui devrait permettre de transférer un débit maximal de 256 Go/s dans une configuration à 16 liens (x16).

Le standard PCIe 6.0 est considéré comme essentiel aux concepteurs de puces-systèmes SoC et aux architectes système qui développent les circuits intégrés de nouvelle génération aptes à transférer des flux massifs de données au sein d’équipements divers et variés dans les domaines comme le calcul à hautes performances (HPC), l’intelligence artificielle et l’apprentissage automatique, le stockage, les réseaux d’entreprise et l’automobile.

Afin de doubler la bande passante par rapport à la version PCIe 5.0, la technologie PCIe 6.0 utilise la modulation PAM-4 (Pulse Amplitude Modulation – 4 Levels) qui permet de traiter 2 bits par cycle au lieu d’un seul pour la modulation NRZ. Pour compenser le taux d’erreur binaire BER plus élevé qui en résulte, la spécification PCIe 6.0 met en œuvre un codage FEC (Forward Error Correction) associé à un contrôle de redondance cyclique CRC. Le nouveau standard spécifie par ailleurs une nouvelle structure fixe de paquets pour l’échange de données sous le nom de mode Flit (Flow Control Unit), la modulation PAM-4 et le codage FEC ne fonctionnant que sur des paquets de données de longueur fixe (256 octets ici).

Selon l’organisation PCI-SIG, les premiers produits mettant en œuvre la technologie PCIe 6.0 devraient arriver sur le marché dans les douze à dix-huit mois qui viennent.

-dissolve-basic-fr.jpg)