Créée en 2019 sous la houlette de la Fondation Linux, l’alliance Chips annonce la mise à disponibilité de tous, gratuitement, des cœurs de processeur RISC-V SweRV Core EH2 et SweRV Core EL2 développés pour la communauté open source par Western Digital. ...On rappellera que l’alliance Chips, lancée par des sociétés comme Google, SiFive, Western Digital et Esperanto Technologies, a pour objectif de développer, dans le cadre d’un environnement collaboratif, un jeu de blocs d’IP et d’outils open source facilitant la conception de processeurs et de puces-systèmes SoC bâtis sur l’architecture, également open source, RISC-V. Et ce sur des marchés aussi divers que les terminaux mobiles, l’informatique, l’électronique grand public et l’Internet des objets.

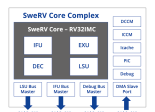

Depuis l'introduction des IP SweRV Core EH2 et SweRV Core EL2 plus tôt cette année, l'alliance Chips assure avoir travaillé avec sa communauté pour valider de manière exhaustive les cœurs à travers un processus transparent et rigoureux, et pour y intégrer plusieurs mises à jour. Le SweRV Core EH2, présenté comme le premier cœur embarqué RISC-V commercial à double thread, est conçu pour les équipements prenant en charge des applications fortement consommatrices de données dans des domaines comme la périphérie de réseau (edge), l'intelligence artificielle (IA) et l'Internet des objets (IoT). Le SweRV Core EL2, quant à lui, est un cœur RISC-V très compact à ultrafaible consommation optimisé pour des applications telles que les séquenceurs de machines d'état et les générateurs de formes d'onde.

« Notre travail qui a consisté à apporter à la communauté open hardware les nouveaux cœurs SweRV Core EL2 et EH2 est une étape supplémentaire vers notre objectif qui est d'accélérer l'innovation RISC-V, indique Zvonimir Bandić, président de la Chips Alliance. Nous avons déjà constaté un fort intérêt de l'industrie pour le SweRV Core EH1 et nous offrons désormais deux options supplémentaires aux ingénieurs qui conçoivent des applications IoT, grand public, mobiles et embarquées en général. »

A noter que l’alliance Chips organise demain 20 mai (21 mai en Europe) un événement en ligne où seront détaillés les cœurs SweRV Core EH2 et EL2 ainsi que les logiciels et solutions ad hoc pour les programmeurs.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV