La firme taïwanaise Andes Technology, membre fondateur de la Fondation RISC-V, s'est lancée dans un partenariat technologique avec l’américain Dover Microsystems, éditeur d’une solution de sécurisation de processeurs par le biais d’un bloc d’IP.... Pensée pour immuniser les processeurs contre des attaques malveillantes menées au travers d’un réseau, la solution développée par les deux sociétés vise à à fournir une solution spécifique pour les coeurs RISC-V, fondée sur la technologie CoreGuard de Dover. Il s’agit d’un bloc de propriété intellectuelle capable de bloquer instantanément des instructions qui violent des règles de sécurité préalablement établies, permettant ainsi aux processeurs embarqués de se défendre par eux-mêmes contre des vulnérabilités logicielles et des attaques menées à travers des réseaux de communication.

La technologie IP CoreGuard de Dover s’intègre aux processeurs RISC-V d’Andes pour les protéger, selon les deux sociétés, contre 94% des vulnérabilités logicielles connues, notamment des dépassements de mémoire tampon, l’injection de code, l’exfiltration de données et les violations de sécurité (préalablement renseignées, toutefois).

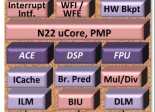

Les processeurs RISC-V d’Andes reposent sur l'architecture AndeStar V5 qui maintient la compatibilité avec la technologie RISC-V et hérite ainsi de ses avantages connus : compacité, modularité et possibilité d’extensions. Les cœurs Andes RISC-V comprennent les coeurs 32 bits N22 ultracompacts pour des applications telles que les microcontrôleurs d’entrée de gamme, les cœurs 32 bits D25F pour les applications de traitement du signal, les N25F/X25F à 32 ou 64 bits pour le contrôle à grande vitesse de tâches de calcul intensives (dont les opérations à à virgule flottante), les A25/AX25 pour les applications Linux et enfin les A25MP/AX25MP pour les applications multicœurs à cohérence de cache.

Quant au bloc d’IP sur silicium CoreGuard (fourni sous forme de code RTL écrit en SystemVerilog) de Dover Microsystems, il surveille chaque instruction exécutée afin de s’assurer qu’elle est conforme à un ensemble défini de règles de sécurité et de confidentialité, traçant au niveau du comportement du processeur une frontière précise entre ce qui est autorisé et ce qui ne l’est pas. Si une instruction enfreint une règle (micropolicy), le bloc d’IP CoreGuard Policy l'empêche de s'exécuter avant que tout dommage ne soit causé.

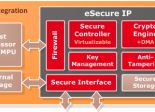

Signalons que sur cet aspect sécurité des architectures RISC-V, Andes collabore déjà avec la société belge Silex Insight qui délivre un bloc d’IP baptisé eSecure qui agit en tant que racine de confiance (root-of-trust) au sein d’un processeur, garantissant l’authenticité et l’intégrité du matériel, du logiciel, des données et du canal de communication de n’importe quel équipement connecté.

Andes s’est aussi engagé dans un partenariat similaire avec la firme française Tiempo Secure afin d’amener l’architecture de processeur RISC-V au niveau des exigences de sécurité CC EAL5+. Et ce à partir de l’offre de Tiempo, un élément sécurisé de niveau EAL5+ présenté sous forme de bloc d’IP et spécifiquement taillé pour les concepteurs de puces-systèmes. Ce bloc d’IP procure notamment des contremesures et des détecteurs de sécurité de niveau EAL5+ aptes à contrer les attaques par intrusion et par canaux auxiliaires.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à la sécurité dans les systèmes embarqués : Embedded-SEC https://www.linkedin.com/showcase/embedded-sec/

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV https://www.linkedin.com/showcase/embedded-riscv/