Membre fondateur de la Fondation RISC-V, le taïwanais Andes Technology a étoffé son catalogue de cœurs RISC-V avec des modèles multicœurs 32 bits et 64 bits dotés, pour la première fois dans l’industrie, d’un jeu étoffé d’instructions DSP. ...Estampillées respectivement A25MP et AX25MP, ces deux IP ciblent les applications exigeantes en performances de calcul comme l’intelligence artificielle et l’assistance à la conduite automobile (ADAS) où il faut également traiter des signaux audio et/ou vidéo et des images.

On notera à cet égard que c’est Andes qui dirige le groupe de travail P-Extension de la Fondation RISC-V, chargé justement d’apporter un jeu d’instructions DSP standard à l’architecture open source RISC-V. Dans ce cadre, le Taïwanais a offert son jeu d’instructions DSP/SIMD comme base de départ et a aligné les A25MP et AX25MP sur le projet de standard. du groupe de travail.

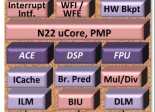

Déclinées dans des versions jusqu’à quatre cœurs RISC-V, les dernières en date des IP d’Andes bénéficient en outre d'un bloc matériel de gestion de la cohérence de cache qui simplifie la conception logicielle. Celui-ci prend en charge la cohérence de la mémoire cache de niveau un, ainsi que celle des entrées-sorties pour les maîtres de bus sans cache, et peut gérer un second niveau de cache optionnel.

Dans la pratique, Ies processeurs A25MP et AX25MP peuvent être cadencés à plus de 1 GHz en technologie 28 nm et prennent en charge Linux en mode SMP (Symmetric Multiprocessing). Andes accompagne ses processeurs dotés d’instructions DSP d’outils ad hoc, comme un compilateur, des bibliothèques DSP et un simulateur.

Ajoutons que le Taïwanais a mis à jour les versions monocœurs des A25MP et AX25MP, les A25 32 bits et AX25 64 bits, avec le jeu d’instructions DSP. La société propose aussi le processeur D25F, qui est un A25 sans unité de gestion mémoire MMU et sans prise en charge du mode hyperviseur (S-mode), pour les applications DSP qui n’ont pas besoin d’exécuter Linux.

Précisons enfin que les outils de développement et les piles logicielles de la firme allemande Segger sont désormais dipsonibles pour les cœurs RISC-V d'Andes (lire aussi notre article ici).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV https://www.linkedin.com/showcase/embedded-riscv/