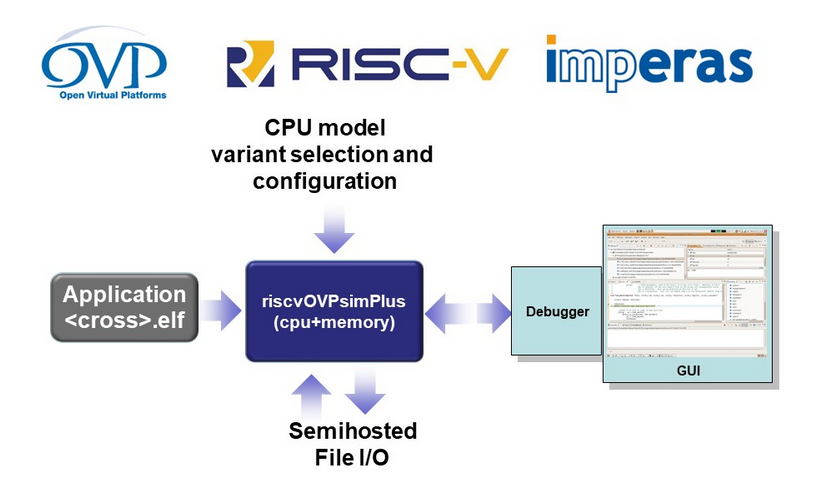

Adapté au développement d’architectures RISC-V, le simulateur riscvOVPsimPlus, précis au niveau instruction, d’Imperas est disponible en accès libre et procure désormais des fonctionnalités de simulation étendues pour le débogage, y compris la trace d'instructions entièrement configurable, la prise en charge du débogage GDB/Eclipse, ainsi que des options de configuration mémoire....

- Simulateur fondé sur la technologie Open Virtual Platform (OVP) d’Imperas

- Modèle intégrant les fonctionnalités CLIC (Core Local interrupt Controller) standard complètes

- Modèle intégrant un mode de débogage, la simulation d'hyperviseur "H", ainsi que les extensions ISA "quasi ratifiées" pour le vectoriel "V"

- Modèle intégrant la manipulation de bits "B" et la cryptographie (Scalar)

- Vitesse de simulation de 2 000 Mips sur une machine hôte sous Linux ou Windows

-dissolve-basic-fr.jpg)