La société avait annoncé en octobre 2022 être devenue un membre stratégique de l’organisme RISC-V International qui promeut à travers le monde l’architecture de processeur open source du même nom. Le français Tiempo, fournisseur d’éléments sécurisés sous forme d'IP et de bibliothèques logicielles sécurisées, concrétise cet engagement en proposant désormais aux développeurs le bloc d’IP Tesic RISC-V Secure Element.

Alors que la sécurité devient un enjeu central de tout développement de puces-systèmes SoC, Tiempo a décidé d'enrichir le socle technologique de la communauté RISC-V avec son expertise dans le domaine de la sécurité en développant cette nouvelle version de son élément sécurisé (SE, Secure Element).

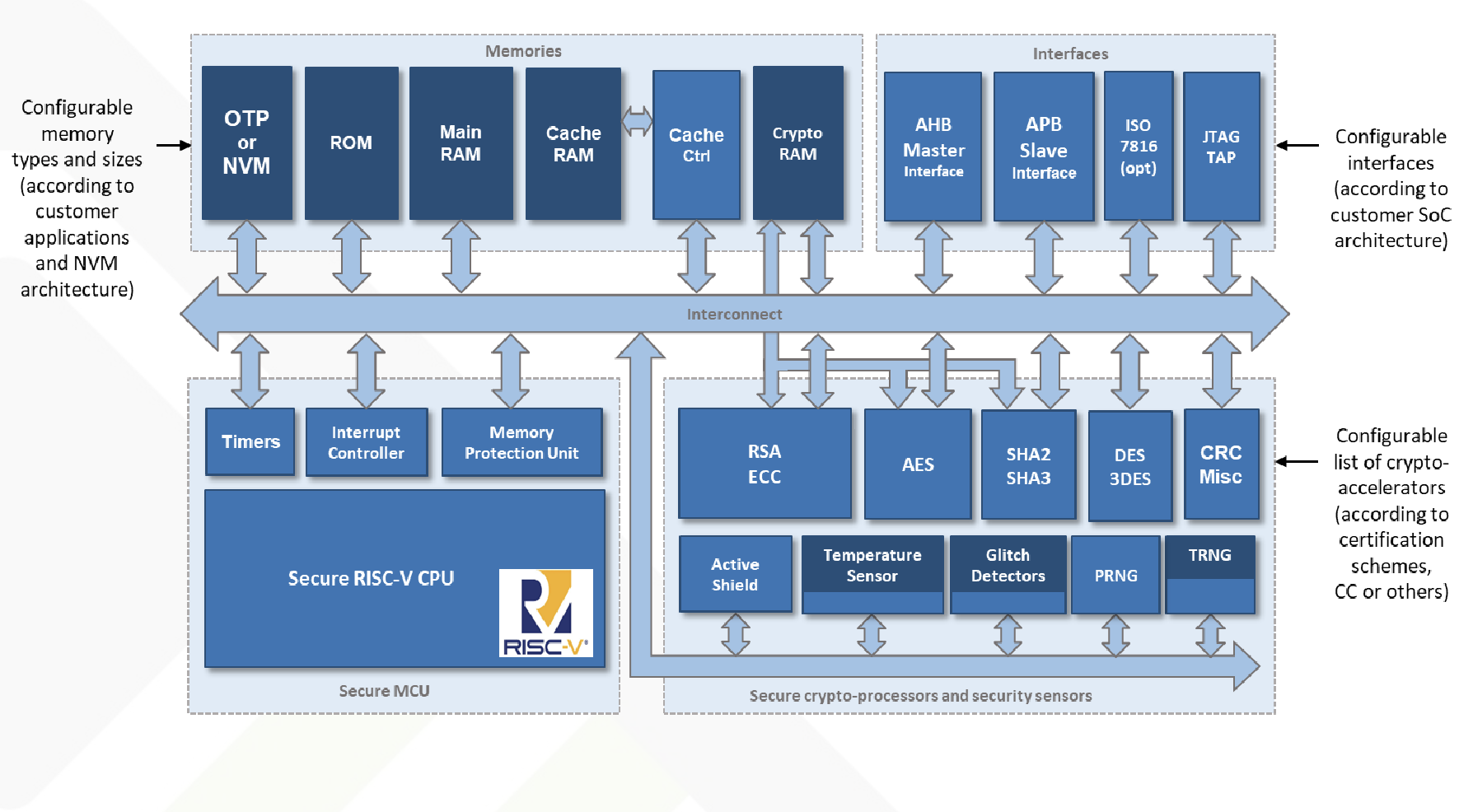

Selon Tiempo, compte tenu de l'évolution mondiale de la sécurité qui migre insensiblement du logiciel vers le matériel, ce développement combine le meilleur des deux mondes car il hérite des fonctionnalités de sécurité du SE Tesic avec les avantages de l'écosystème RISC-V. Avec à la clé une offre étendue d'outils de développement adoptés par une large communauté de développeurs. Le bloc d’IP de Tiempo, qui apporte un niveau de sécurité élevé aux systèmes embarqués, est prêt à être certifié au niveau EAL5+ des Critères communs et est censé rendre le développement de la partie sécurité plus facile grâce à son intégration avec l'écosystème RISC-V. De fait, il est adapté à toute conception nécessitant une enclave sécurisée, un élément sécurisé ou une racine de confiance hautement protégée contre les attaques par canal auxiliaire, par exemple.

Les applications de l'IP de Tiempo incluent les iSIM et iUICC sécurisées et certifiées conformément aux spécifications de la GSMA, le paiement EMVCo, les portefeuilles matériels, l'authentification Web Fido2, les protocoles HSM pour communications V2X, l'accès aux voitures intelligentes, le démarrage sécurisé, les mises à jour over-the-air sécurisées du micrologiciel, le débogage sécurisé...

Dans le détail, le bloc d’IP Tesic RISC-V Secure Element s'appuie sur un cœur de processeur RISC-V 32 bits fondé sur le jeu d'instructions (ISA) RISC-V RV32IMCB. Il hérite des caractéristiques de sécurité de toute la famille des IP Tesic et inclut spécifiquement des capacités sophistiquées de masquage des données, qui protègent les données à la volée, pendant qu'elles sont échangées entre le microcontrôleur et les périphériques. Ce qui procure une protection contre les attaques par canal auxiliaire telles que l'analyse de consommation simple (SPA) ou différentielle (DPA).

L'IP Tesic RISC-V Secure Element comprend également des fonctionnalités de protection des registres, y compris la détection et la correction des erreurs. Le fichier de registre du microcontrôleur et les registres d'état sont protégés contre les perturbations et les attaques parasites, entre autres. Comme elle s'appuie sur la gamme Tesic existante, l'IP est prête à être certifiée pour le niveau EAl5+ des Critères communs CC pour les profils de protection PP 0084 et PP 0117.

Parallèlement, Tiempo Secure a mis au point un kit de développement, permettant à tous les développeurs de cœurs RISC-V de construire leur propre puce-système en bénéficiant de la sécurité apportée par les technologies de la société. Le kit permet notamment aux développeurs d'explorer les fonctionnalités du SE et de développer leur micrologiciel, y compris l'accès à l'élément sécurisé. Le kit comprend le microcontrôleur RISC-V et le Secure Element, ainsi que des outils logiciels : compilateur, éditeur de liens et débogueur fondés sur les logiciels open source GNC GCC/GDB, chaîne d'outils et environnement de développement RISC-V, bibliothèque crypto certifiée CC EAL5+ et EMVCo...

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à la sécurité dans les systèmes embarqués : Embedded-SEC

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-dissolve-basic-fr.jpg)