La société de conception d’IP britannique lowRISC, qui promeut et encourage les approches open hardware et notamment celles liées à l'architecture RISC-V, a réussi à rassembler Google, G+D Mobile Security, Nuvoton, Western Digital et l’Ecole polytechnique fédérale de Zurich autour d’un projet open source baptisé OpenTitan ...dont l’objectif est de spécifier une conception de référence pour puces de sécurité faisant office de racines de confiance ...(Root of Trust, RoT), ainsi que des conseils d’intégration afférents.

Ce type de circuit intégré, rappelons-le, vise à assurer qu’une infrastructure matérielle et le logiciel qui s’y exécute restent dans un état attendu et fiable « digne de confiance » en vérifiant que les composants système critiques se lancent en toute sécurité avec du code autorisé et vérifiable. Une puce RoT est donc à même de vérifier qu’un logiciel de bas niveau n’a pas été infecté par du code malveillant, de fournir une identité unique au sens cryptographique à un équipement, de protéger des secrets comme les clés de chiffrement de façon à ce qu'ils restent résistants aux tentatives de fraude, etc.

La technologie RoT sur silicium développée dans le cadre du projet open source OpenTitan a vocation à être implémentée par des sociétés de semi-conducteurs ou des fournisseurs de plates-formes dans des circuits intégrés pour cartes mères de serveurs, cartes réseau, terminaux utilisateur (PC portables, téléphones mobiles…), routeurs grand public, objets IoT… A ce titre, Google rappelle que la société s’appuie déjà sur une puce RoT maison, estampillée Titan, pour s’assurer que les ordinateurs déployés dans ses centres de données démarrent à partir d’un état de confiance connu avec du code dûment vérifié.

Dans le détail, le projet OpenTitan est supervisé par le britannique lowRISC basé à Cambridge et définit au niveau RTL la conception logique d’une puce RoT sur silicium. Ce design s’articule autour d’un cœur de processeur open source (en l’occurrence le cœur RISC-V Ibex initialement conçu par l’Ecole polytechnique fédérale de Zurich et récupéré par lowRISC en début d’année), de coprocesseurs cryptographiques, d’un générateur de nombres aléatoires, de hiérarchies mémoire pour le stockage volatil et non volatil, de mécanismes de défense, de périphériques d’entrées/sorties et d’un amorçage sécurisé, entre autres.

Dans le détail, le projet OpenTitan est supervisé par le britannique lowRISC basé à Cambridge et définit au niveau RTL la conception logique d’une puce RoT sur silicium. Ce design s’articule autour d’un cœur de processeur open source (en l’occurrence le cœur RISC-V Ibex initialement conçu par l’Ecole polytechnique fédérale de Zurich et récupéré par lowRISC en début d’année), de coprocesseurs cryptographiques, d’un générateur de nombres aléatoires, de hiérarchies mémoire pour le stockage volatil et non volatil, de mécanismes de défense, de périphériques d’entrées/sorties et d’un amorçage sécurisé, entre autres.

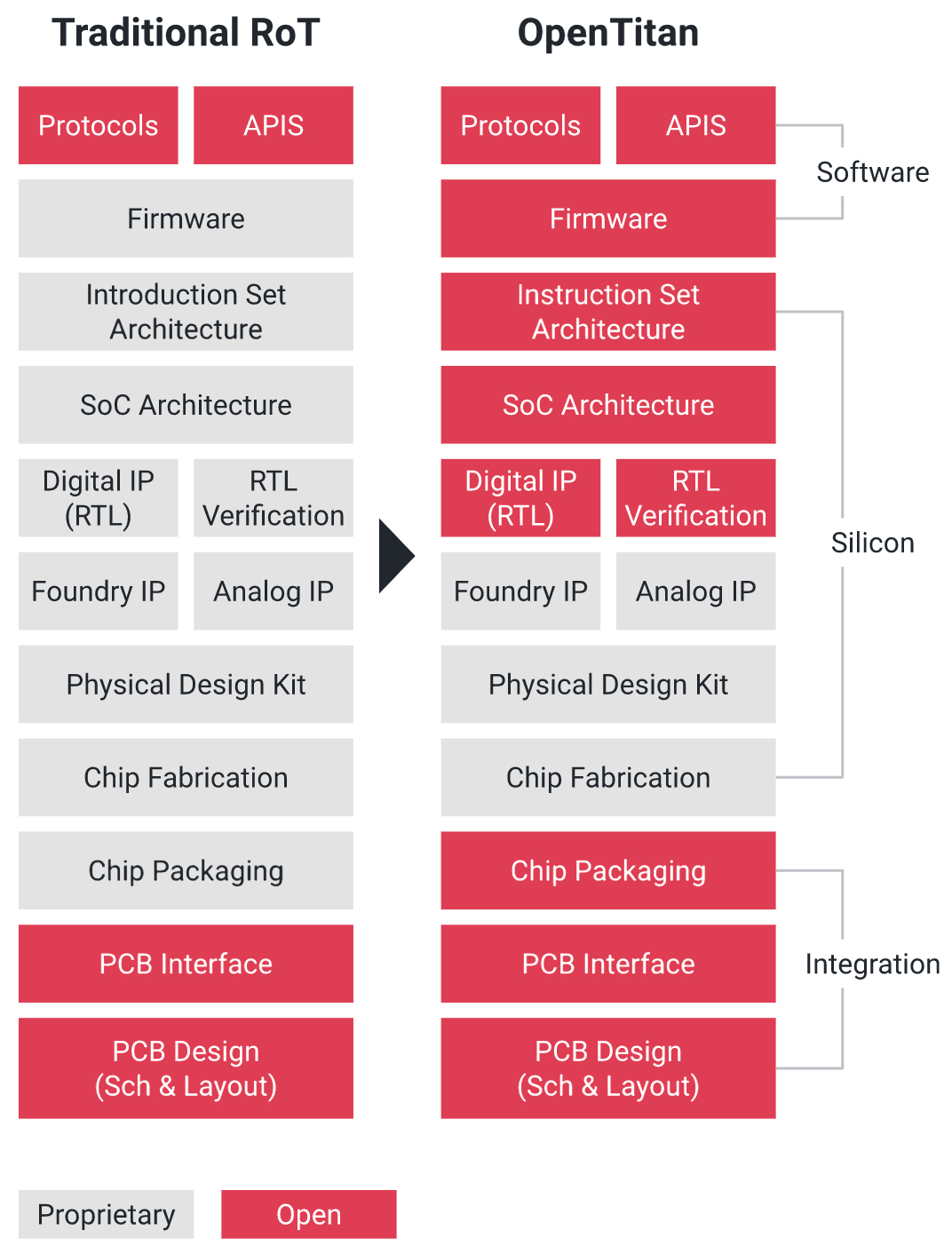

Selon les membres fondateurs du projet OpenTitan, les fabricants de puces et les fournisseurs de plates-formes qui adopteront le framework open source pourront inspecter le code RTL et contribuer à l’amélioration du design, du firmware et de la documentation associée de manière totalement transparente.

« On attend aujourd'hui des utilisateurs qu’ils mettent leur confiance dans des puces RoT propriétaires pour des systèmes parfois critiques, sans qu’ils aient la capacité de les examiner et de les appréhender dans leur totalité, indique Dominic Rizzo, directeur du projet OpenTitan. En créant OpenTitan avec une communauté de partenaires industriels et économiques, nous pouvons profiter du savoir-faire et des principes de sécurité utilisés lors du développement des puces Titan de Google pour élaborer des conceptions RoT accessibles à l’ensemble de l’industrie. La sécurité ne devrait en effet jamais s’appuyer sur l’opacité. »

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à la sécurité dans les systèmes embarqués : Embedded-SEC https://www.linkedin.com/showcase/embedded-sec/

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV https://www.linkedin.com/showcase/embedded-riscv/