En octobre 2015, on s’en souvient, Renesas lançait deux familles de microcontrôleurs 32 bits qui s’avéraient les premiers dans la gamme du fabricant de semi-conducteurs à être basés sur un cœur ARM Cortex-M ...(le Cortex-M4 en l’occurrence) et à être couplés avec la plate-forme logicielle Synergy. Une plate-forme qui intègre une suite complète de logiciels et d’API et dont l’objectif est avant tout de raccourcir les temps de développement de produits pour l'Internet des objets.

Renesas poursuit aujourd’hui cette stratégie en dévoilant une troisième famille de microcontrôleurs Synergy (les S124 à cœur ARM Cortex-M0+), caractérisés par une consommation ultrafaible et accompagnés de versions mises à jour de la suite Synergy Software Package (SSP) et de l'outil de développement e2studio. Dans le détail, les S124 se caractérisent par une consommation de 70,3 µA/MHz et intègrent des convertisseurs A/N 14 bits, des convertisseurs N/A 12 bits, des comparateurs éco-efficaces, plus de 30 canaux d'entrée pour capteurs tactiles capacitifs, des interfaces USB et CAN et des mécanismes de sécurité (contrôle de parité SRam, générateur de nombres aléatoires, cryptographie AES-256). Applications typiques visées : les capteurs intelligents des nœuds de bordure IoT, le contrôle dans les appareils électroménagers et les terminaux de point de vente.

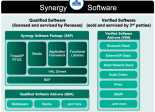

La version SSP 1.1.0 supportée par la nouvelle famille de microcontrôleurs dispose notamment d’optimisations spécifiques pour le système d'exploitation temps réel ThreadX et la pile de communication USB-X afin de répondre aux contraintes de capacité mémoire des microcontrôleurs S124. L’outil e2Studio v5.0 est, quant à lui, désormais basé sur la dernière mise à jour Eclipse v4.5 (release Mars) et comprend en plus de nombreuses fonctionnalités pour améliorer le guidage automatique lors du démarrage de nouveaux projets avec la plate-forme Synergy, telles que la présentation de tous les blocs constitutifs d'un projet sous la forme d’une pile graphique afin de simplifier le flux de conception et fournir en un seul coup d'œil une visibilité complète sur l'utilisation globale de la mémoire.