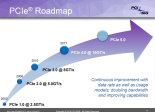

Le français PLDA Group estime être le premier sur le marché à proposer un contrôleur de bus PCI Express 4.0 (dans la version 0.9) sous la forme d’un bloc d’IP à implanter dans un FPGA. Rappelons que la spécification PCI Express 4.0 est en cours de finalisation au sein de l’organisme PCI-SIG... avec l’objectif d’une publication de la version finale avant la fin de l'année (à l’origine le PCI-SIG avait prévu sa sortie en avril de cette année).

Le PCI Express 4.0 va permettre un doublement du débit par rapport à la version 3.0, soit 16 gigatransferts/s avec un codage 128b/130b, l’équivalent de 2 Go/s pour chaque liaison bidirectionnelle sur pistes en cuivre.

La solution de PLDA se présente sous la forme de deux blocs d’IP, le XpressRICH4 et le XpressRICH4-AXI, pour les FPGA Virtex Ultrascale+ de Xilinx. Selon la société, ces contrôleurs de bus PCI Express 4.0 prennent en charge l’ensemble des dernières spécifications émises par le PCI-SIG, y compris la technologie EIEOS (Electrical Idle Exit Ordered Set). Les caractéristiques du bus ont été validées à 16 gigatransferts/s sur une plate-forme x86 avec un trafic de données en mode DMA (Direct Memory Access) de bout en bout.

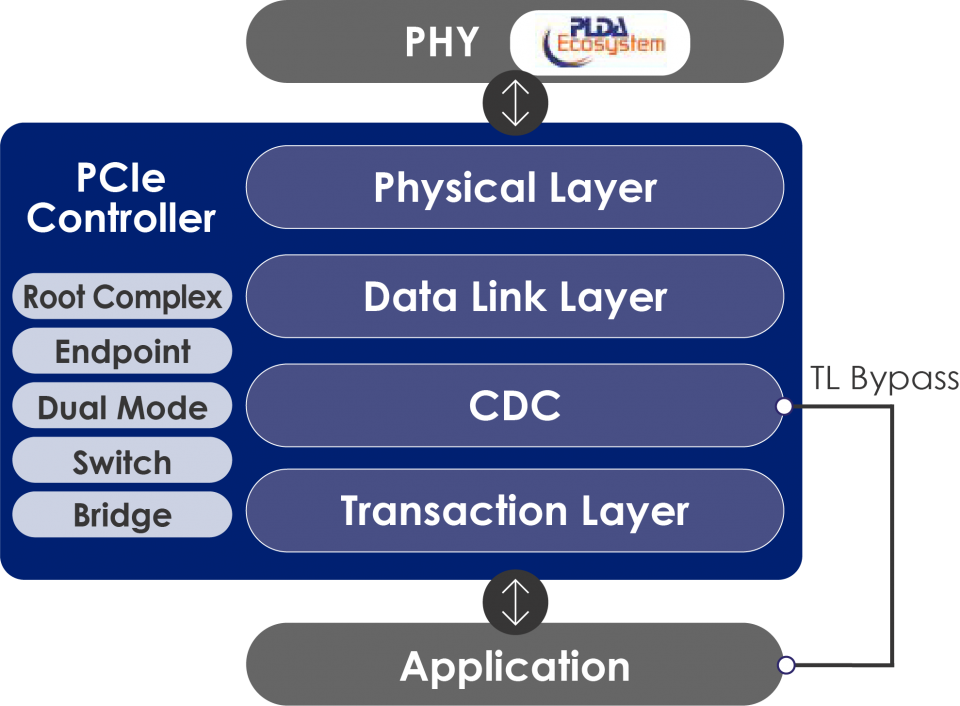

L’XpressRICH4 est une interface PCIe 4.0 présentée sous forme de bloc d'IP logiciel capable d'offrir des caractéristiques avancées telles que le SR-IOV (Single Root Inpout Output Virtualization, soit le partage de ressources entre plusieurs machines virtuelles) ou la protection des données (mécanismes ECC et ECRC).

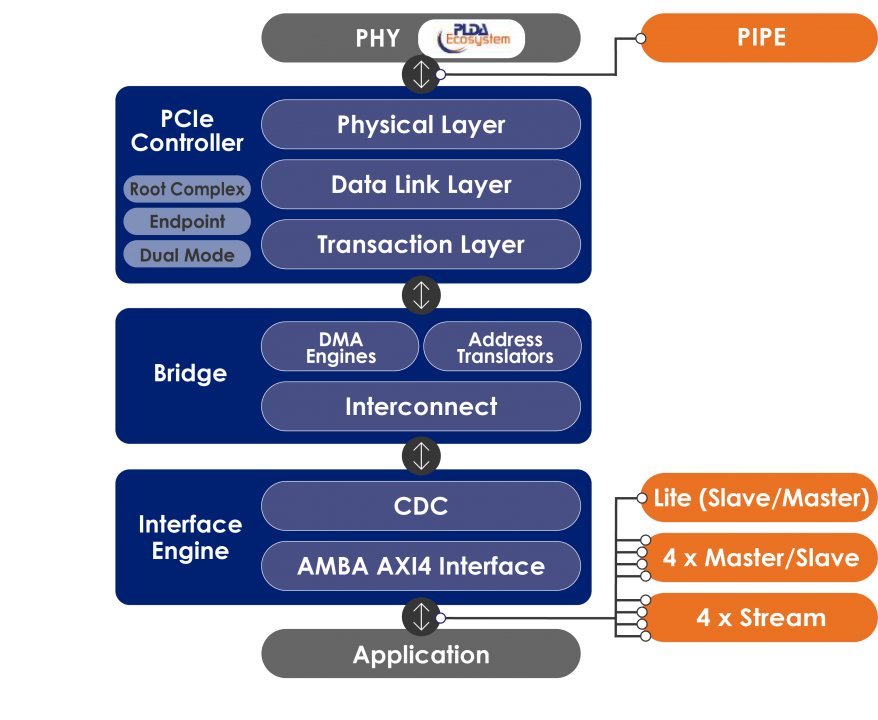

Quant au bloc XpressRICH4-AXI, il s’agit d’une interface PCIe 4.0 dotée dune interface utilisateur programmable Amba AXI3/AXI4 qui affiche des performances élevées au niveau des performances de transferts DMA.