Les sociétés Rambus, PLDA et Avery Design ont associé leurs compétences respectives pour proposer une solution PCI Express (PCIe) 4.0 complète et prévalidée dans le silicium, disponible pour la plupart des procédés de gravure Cmos. ...Cette solution combine un bloc PHY SerDes de Rambus, un contrôleur PCIe de PLDA et une IP de vérification d’Avery Design ; elle intéressera au premier chef les concepteurs d’Asic et de circuits intégrés de type SoC.

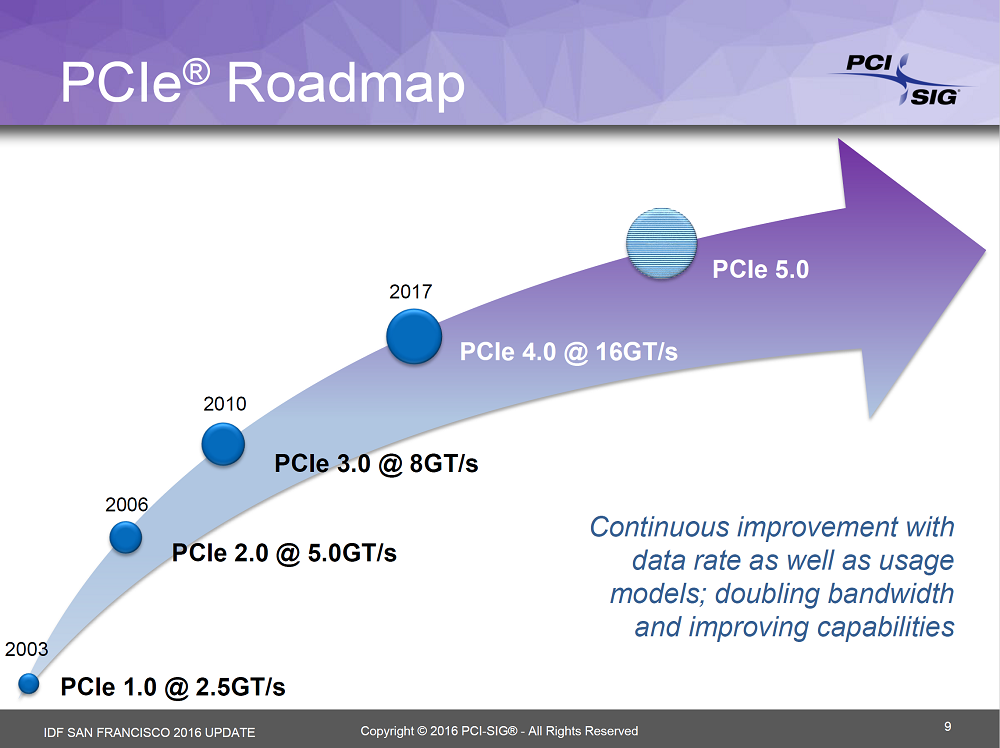

On rappellera que les travaux de standardisation de la version 4.0 du standard PCI Express, mis en branle il y a plus de cinq ans par le groupement d’intérêt spécifique PCI (PCI-SIG), vont bientôt s’achever. La spécification PCIe 4.0, qui va porter le début du célèbre bus série à 16 gigatransferts par seconde (GT/S) par lien unidirectionnel et donc doubler les performances du PCIe 3.0, devrait selon toute probabilité être publiée au troisième trimestre de de cette année (alors que la date d’avril avait été préalablement avancée). Les fournisseurs de blocs d’IP précurseurs de la norme comme PLDA, Synopsys ou Cadence ont d’ailleurs déjà procédé à quelques annonces en la matière (lire notre article ici), tout comme certains fabricants d’instruments de test et de mesure à l’instar de Teledyne LeCroy et Tektronix.

On rappellera que les travaux de standardisation de la version 4.0 du standard PCI Express, mis en branle il y a plus de cinq ans par le groupement d’intérêt spécifique PCI (PCI-SIG), vont bientôt s’achever. La spécification PCIe 4.0, qui va porter le début du célèbre bus série à 16 gigatransferts par seconde (GT/S) par lien unidirectionnel et donc doubler les performances du PCIe 3.0, devrait selon toute probabilité être publiée au troisième trimestre de de cette année (alors que la date d’avril avait été préalablement avancée). Les fournisseurs de blocs d’IP précurseurs de la norme comme PLDA, Synopsys ou Cadence ont d’ailleurs déjà procédé à quelques annonces en la matière (lire notre article ici), tout comme certains fabricants d’instruments de test et de mesure à l’instar de Teledyne LeCroy et Tektronix.

« Notre collaboration avec PLDA et Avery Design se cristallise par un sous-système PCIe complet, indique Luc Seraphin, directeur général de la division Mémoire et interfaces de Rambus. Notre gamme de blocs PHY SerDes est optimisée au niveau consommation et éco-efficacité et s’avère apte à répondre aux exigences d’une large gamme d’applications dont les infrastructures réseau, les centres de données et la calcul hautes performances. »

A noter que Xilinx et IBM ont tout récemment réussi à démontrer l’interopérabilité PCIe 4.0 entre un FPGA UltraScale+ gravé en 16 nm et un processeur Power9, une première dans le domaine des circuits programmables, assurent les deux sociétés. Le Power9 est un processeur à 24 cœurs qui embarque huit milliards de transistors sur une puce fabriquée en technologie FinFET 14 nm sur SOI (silicium-sur-isolant).

-dissolve-basic-fr.jpg)