Quelques mois après avoir levé le voile sur une nouvelle génération de microcontrôleurs 32 bits estampillée MCX (lire notre article), NXP a annoncé hier 2 novembre les premiers modèles de la gamme MCX N destinés à simplifier la conception d’applications intelligentes et sécurisées en périphérie de réseau (edge), notamment dans les domaines de l’Internet des objets et de l’industriel.

Pour rappel, le portefeuille MCX se déclinera à terme en quatre gammes, les MCX N (Advanced), les MCX A (Essential), les MCX W (Wireless) et les MCX L (Ultra-Low-Power). Les microcontrôleurs MCX N se distinguent en particulier par la présence d’une unité de traitement neuronal (NPU) spécifique, développée par la société batave, et destinée à accélérer les inférences en local en assurant une capacité d’apprentissage automatique jusqu’à 30 fois plus performante que celle d’un cœur de microcontrôleur seul. On y trouve aussi un sous-système de sécurité EdgeLock intégré.

D’un point de vue architectural, les MCX N se déploient autour d’un système à double cœur qui associe un cœur Arm Cortex-M33 complet à un autre cœur Cortex-M33 simplifié pour la gestion des fonctions de contrôle (*). Une approche qui permet aux développeurs d’exécuter des applications en parallèle ou de réduire la consommation en éteignant l’un ou l’autre des cœurs en fonction des besoins. A titre d’exemple, dans des applications IoT sécurisées comme des communications pour les mises à jour over-the-air (OTA), le cœur principal peut se charger de la sécurité système tandis que les fonctions de contrôle s’exécutent sur le cœur « allégé ».

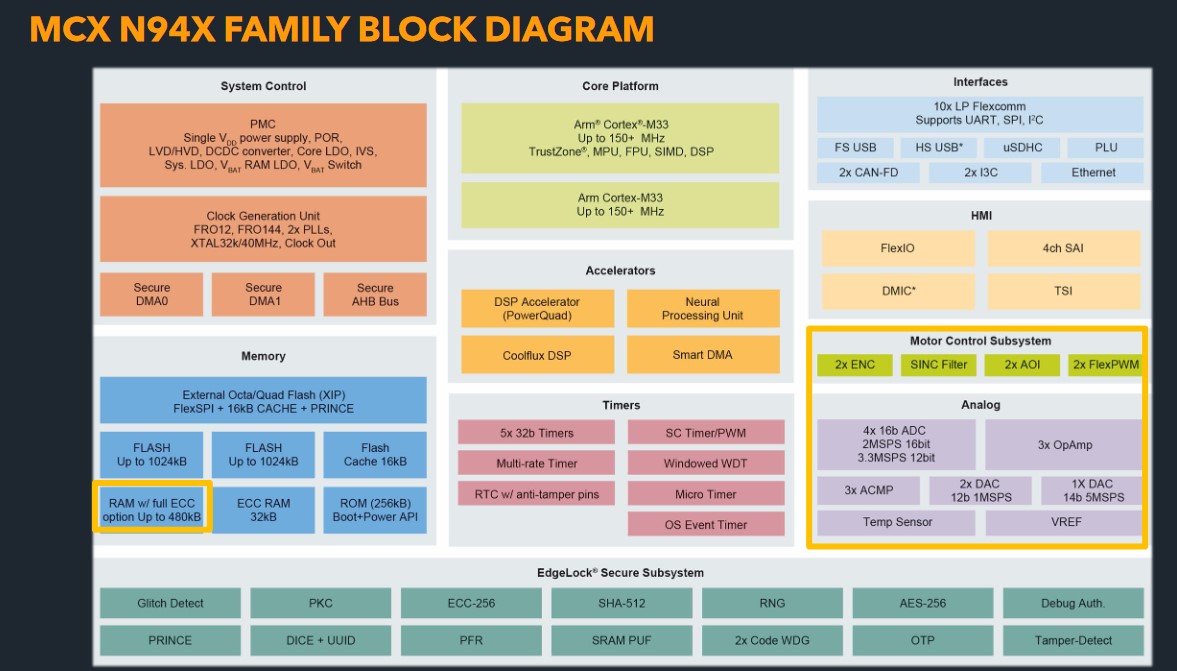

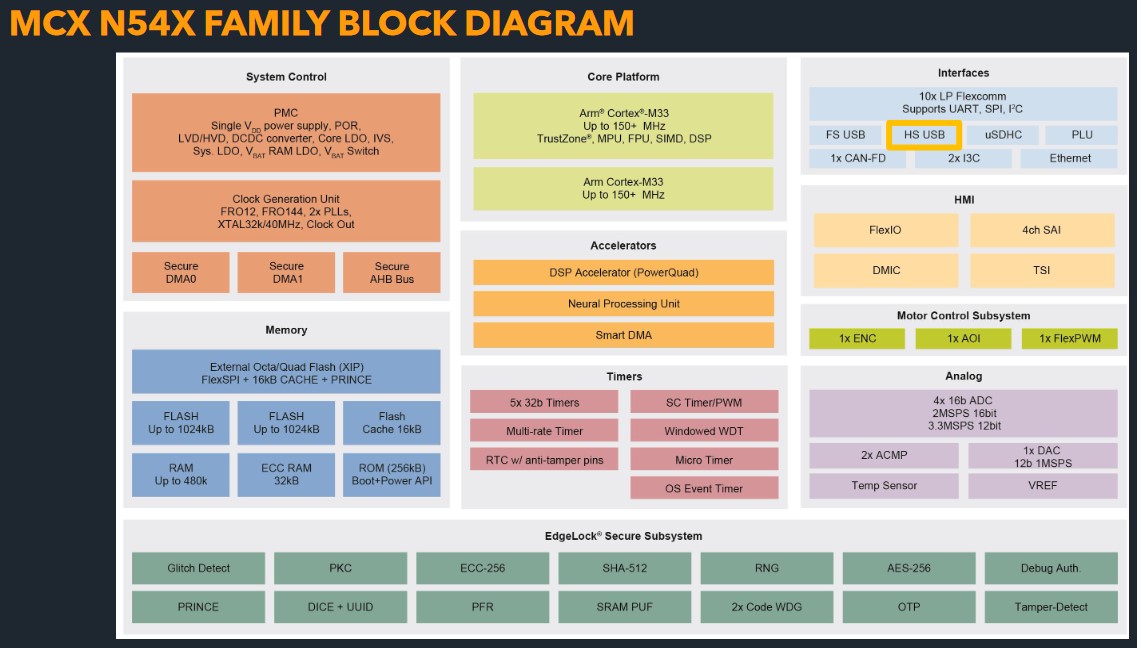

Dans la pratique, NXP compte échantillonner dans le courant du premier trimestre 2023 les microcontrôleurs des familles MCX N94x et MCX N54x dotés de cœurs Cortex-M33 cadencés jusqu'à 150 MHz, de 2 Mo de mémoire flash avec RAM ECC en option, d’un coprocesseur DSP pour le traitement de l’audio et de la voix, et du moteur neuronal NPU cité plus haut. Des coprocesseurs et accélérateurs y sont également mis en œuvre pour réduire la consommation globale d'énergie.

L’apprentissage et le déploiement de modèles d’apprentissage automatique sur le NPU intégré pourront se faire grâce aux outils fournis par l’environnement de développement de logiciels ad hoc eIQ de NXP.

Les deux modèles MCX N94x et MCX N54x diffèrent par le jeu de périphériques proposés. Le premier dispose d'un large variété de périphériques analogiques et de commande moteur avancés, tandis que le second est doté d’interfaces d’entrées/sorties du type USB High Speed (HS) avec couche PHY intégrée, SD ou carte à puce, adaptées aux besoins des applications IoT et grand public.

Tous les microcontrôleurs MCX N sont pris en charge par la suite MCUXpresso de logiciels et d’outils de développement de systèmes embarqués de NXP, utilisée jusqu’à aujourd’hui pour les familles de microcontrôleurs LPC (héritées des racines de la société dans le groupe néerlandais Philips) et Kinetis (issue du rachat de l’américain Freescale fin 2015). Les développeurs peuvent choisir de travailler avec l’IDE MCUXpresso complet ou avec les IDE tierces parties IAR et Keil.

(*) Une telle architecture a déjà été mise en œuvre dans certains microcontrôleurs 32 bits de la famille LPC de NXP, notamment les LPC55S6x.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée aux microcontrôleurs : Embedded-MCU