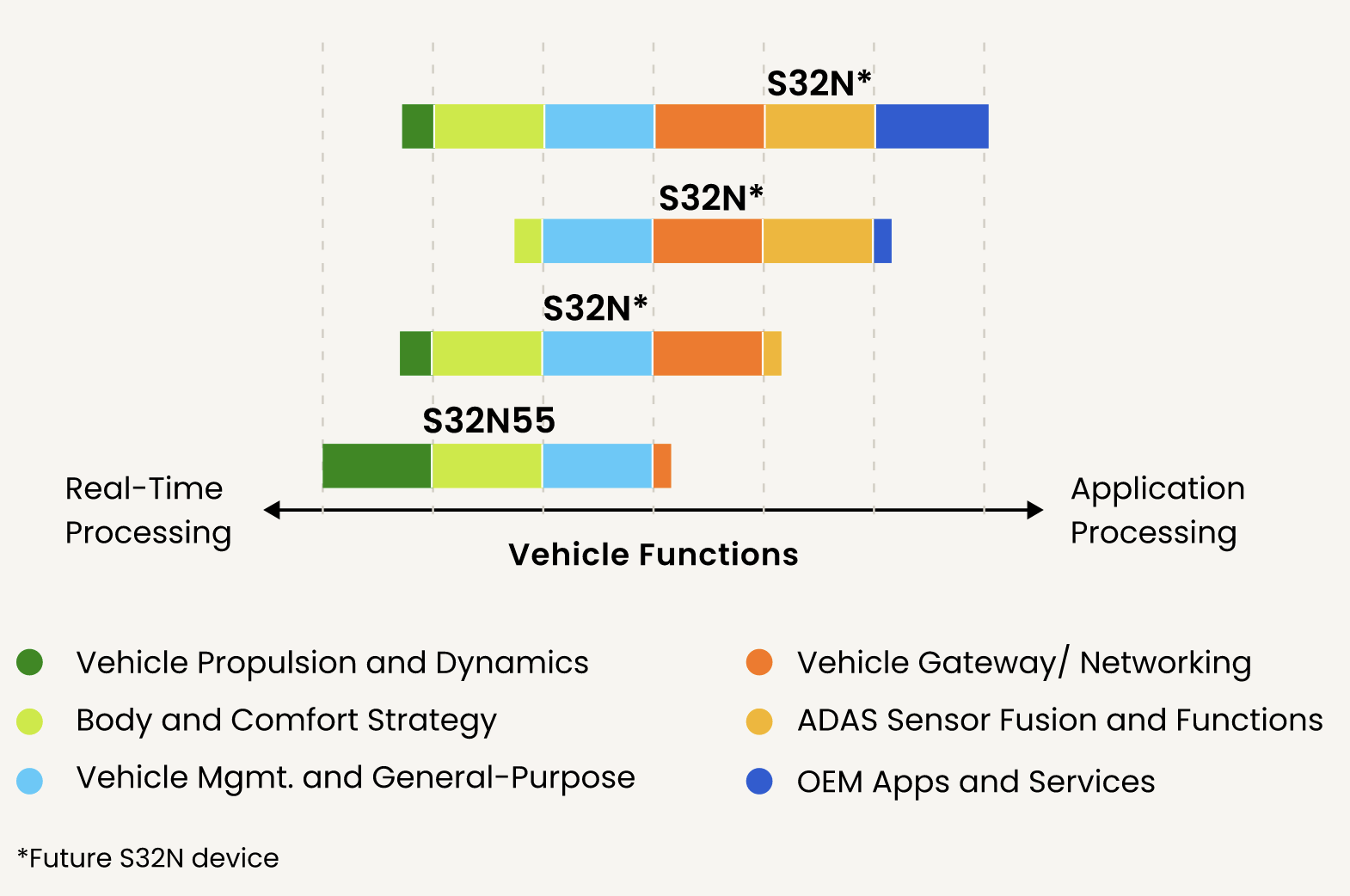

Estampillé S32N55, le premier membre de la famille S32N des processeurs conçus pour la plateforme ouverte S32 CoreRide dévoilée récemment par NXP (voir notre article) et destinée aux développements des véhicules définis par logiciel a été officiellement présenté par la société lors du salon Embedded World qui s’est tenu à Nuremberg du 9 au 11 avril.

Pour rappel la plate-forme S32 CoreRide est présentée par NXP comme une “superintégration” entre un processeur et un ensemble de logiciels embarqués (système d’exploitation temps réel, hyperviseur, piles logicielles de communication, pilotes…) qui vise le contrôle centralisé temps réel et sécurisé d’un véhicule. A travers plusieurs environnements d'exécution isolés par logiciel et renforcée par le matériel (grâce une couche de virtualisation), cette solution peut héberger plusieurs dizaines de fonctions du véhicule avec différents niveaux de criticité, tout en évitant les interférences entre elles. Chaque fonction peut être gérée indépendamment, y compris au niveau de la gestion des pannes, de la réinitialisation et des opérations de mises à jour logicielles OTA granulaires.

« Le processeur S32N55 est le cerveau central du contrôle des véhicules en temps réel dans notre nouvelle plateforme S32 CoreRide, explique Ray Cornyn, vice-président senior et directeur général en charge des processeurs automobiles chez NXP. Grâce à une combinaison de performances au niveau temps réel, d’isolation matérielle critique et de capacités réseau, ce processeur peut héberger plus de fonctionnalités avec moins de circuits, en offrant une évolutivité pour aider à pérenniser les développements de véhicules définis par logiciel. »

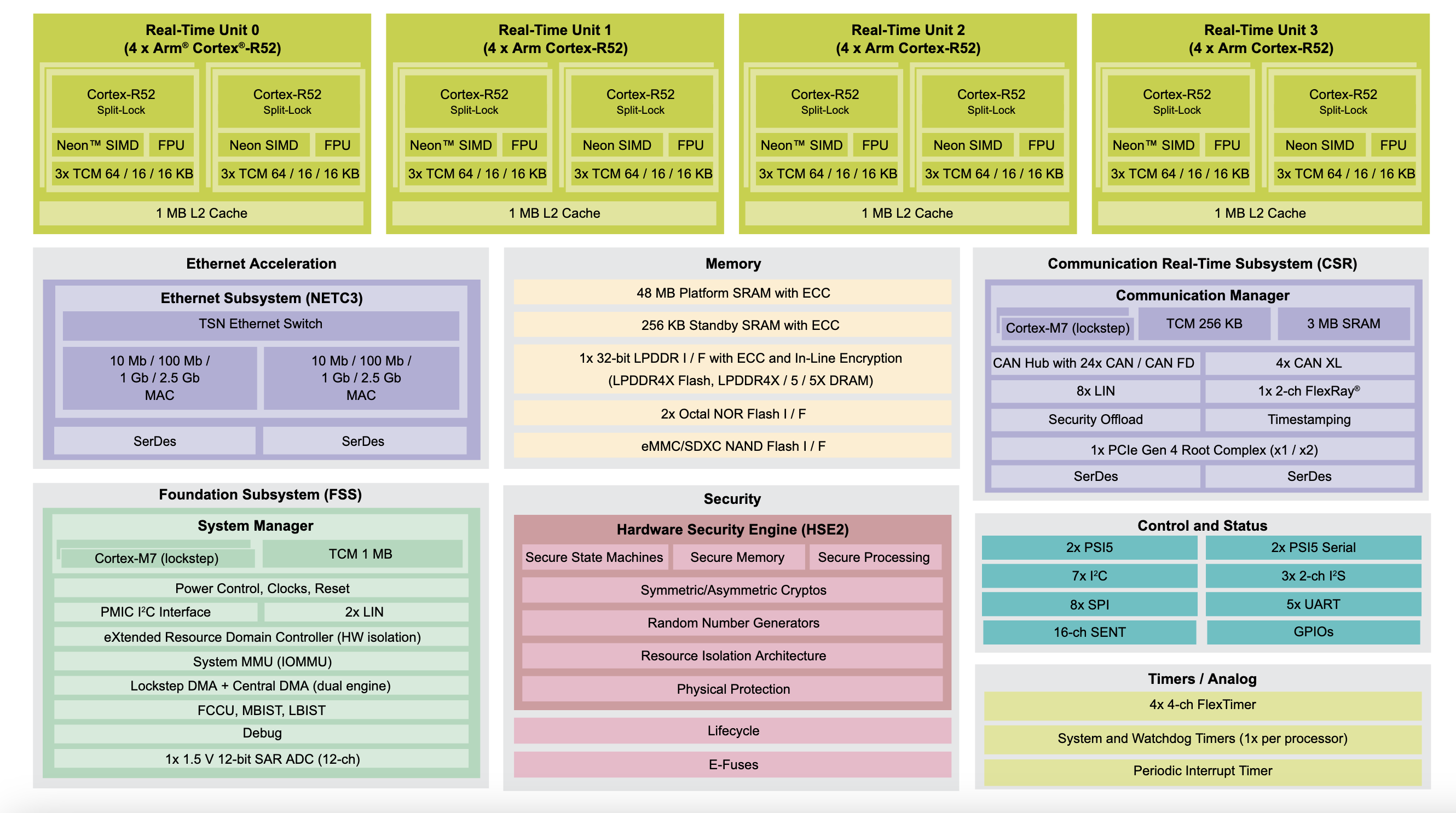

Dans le détail, le processeur S32N55 intègre jusqu’à 16 cœurs de processeur Arm Cortex-R52 en mode "split-lock" (*) fonctionnant à 1,2 GHz pour les traitements temps réel. Les cœurs peuvent fonctionner en modes "split" ou "lock" pour prendre en charge différents niveaux de sécurité fonctionnelle conformément aux exigences de la norme ISO 26262 jusqu’au niveau Asil-D. Deux paires auxiliaires de cœurs en mode lockstep Cortex-M7 prennent par ailleurs en charge la gestion système et des communications.

Dans le détail, le processeur S32N55 intègre jusqu’à 16 cœurs de processeur Arm Cortex-R52 en mode "split-lock" (*) fonctionnant à 1,2 GHz pour les traitements temps réel. Les cœurs peuvent fonctionner en modes "split" ou "lock" pour prendre en charge différents niveaux de sécurité fonctionnelle conformément aux exigences de la norme ISO 26262 jusqu’au niveau Asil-D. Deux paires auxiliaires de cœurs en mode lockstep Cortex-M7 prennent par ailleurs en charge la gestion système et des communications.

La SRam intégrée affiche une capacité de 48 Mo assurant une exécution rapide des applications avec des accès à faible latence en association avec de la mémoire étroitement couplée aux coeurs Cortex-R52 (voir illustration ci-dessous). La mémoire peut être étendue grâce aux interfaces DRam LPDDR4X/5/5X, flash LPDDR4X et flash Nand/NOR.

Les exigences fonctionnelles en matière de sûreté et de sécurité sont prises en charge par le biais de mécanismes de correction des erreurs mémoire et de chiffrement en ligne. Un moteur de sécurité matériel avec pare-feu fournit en outre une racine de confiance pour le démarrage sécurisé, les services de sécurité et la gestion des clés.

Côté communication, un commutateur Ethernet Time-Sensitive Networking (TSN) à 2,5 Gbit/s est intégré, ains qu’un hub CAN pour un routage interne de jusqu’à 24 bus CAN FD et quatre interfaces CAN XL. Une interface PCI Express Gen4 vise à contribuer aussi à la réduction des coûts de câblage.

Le S32N55 est complété par une puce de gestion sécurisée de l'alimentation système qui prend en charge l’aspect sécurité fonctionnelle d’un système, jusqu’au niveau Asil-D, combinée à un circuit d'alimentation principale, l'ensemble procurant aux développeurs une conversion de puissance à haut rendement, la gestion des modes basse consommation ainsi que le séquençage de l'alimentation.

(*) Le mode split-lock offre la possibilité de configurer le système à l’amorçage, soit en mode « split » avec des cœurs indépendants utilisables pour différentes tâches et applications, soit en mode « lock » (avec deux cœurs fonctionnant alors en parallèle pour satisfaire les applications à fortes contraintes de sûreté de fonctionnement).