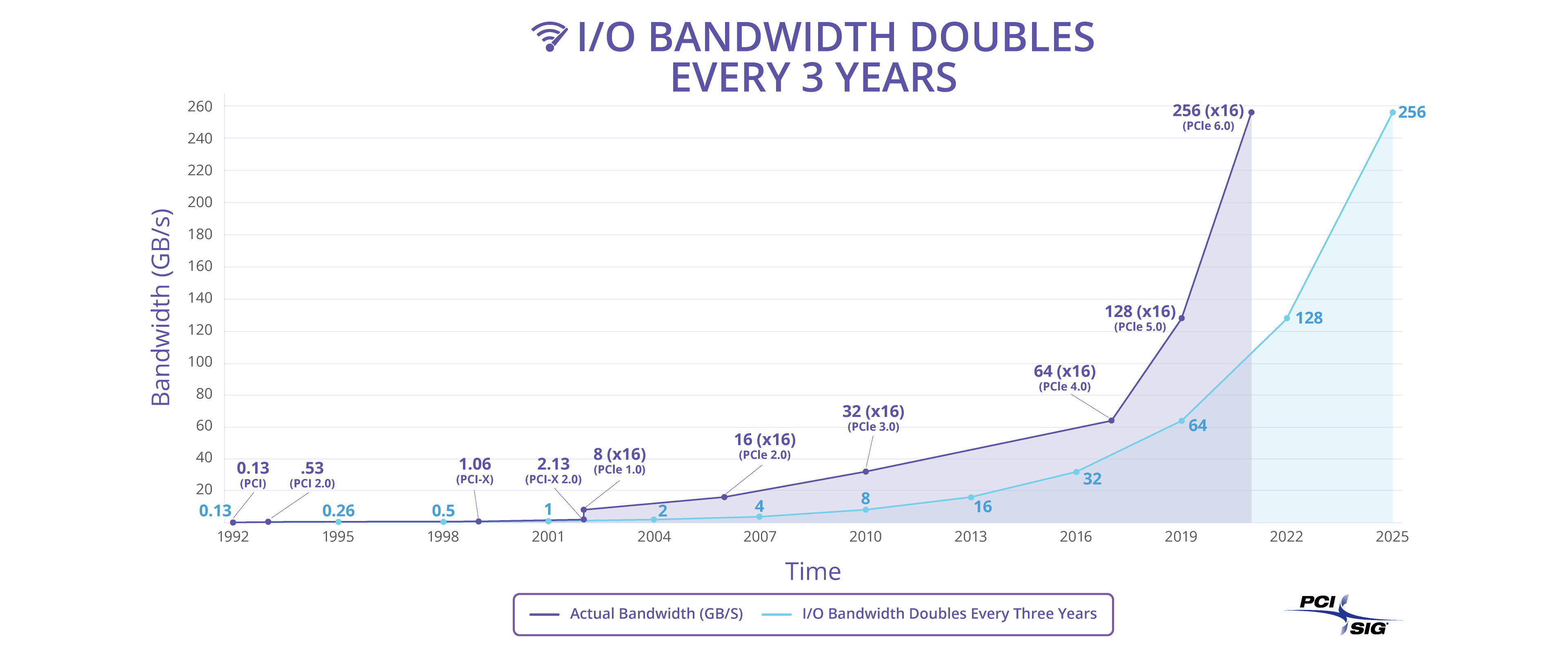

La spécification PCI Express 5.0 tout juste publiée, le groupement d’intérêt spécifique PCI (PCI-SIG) s’est déjà attelé aux travaux de définition d’un futur standard PCI Express 6.0 qui portera cette fois-ci la vitesse du vénérable bus d’entrées/sorties à 64 gigatransferts par seconde par lien unidirectionnel ...(contre 32 GT/s pour le PCIe 5.0), tout en maintenant des caractéristiques de basse consommation et la rétrocompatibilité avec les générations précédentes.

Le PCI-SIG s’est donné pour objectif de boucler ses efforts de standardisation autour du PCIe 6.0 d’ici à 2021.

Certaines caractéristiques de la future version 6.0 ont déjà été arrêtées. Elle devra permettre de transférer un débit maximal de 256 Go/s dans une configuration à 16 liens et utilisera une modulation d’impulsions en amplitude à quatre niveaux PAM-4 (Pulse Amplitude Modulation – 4 Levels) en s’appuyant pour cela sur la technologie 56G PAM-4 déjà mise en œuvre dans l’industrie. Le PCI Express 6.0 inclura aussi un codage correcteur d’erreurs FEC (Forward Error Correction) à faible latence associé à des mécanismes visant à améliorer l’efficacité d’utilisation de la bande passante.

« Au cours des deux dernières décennies, la technologie PCI Express a pu devenir une technologie d’entrées/sorties omniprésente grâce à sa capacité à améliorer sa vitesse au travers de cinq générations de standards, indique Dennis Martin, analyste chez Principled Technologies. Avec la spécification PCI Express 6.0, le PCI-SIG souhaite répondre aux besoins de marchés effervescents comme l’intelligence artificielle, l’apprentissage automatique, les systèmes de communication, le stockage, le calcul à hautes performances HPC, etc. »

-dissolve-basic-fr.jpg)