Le XpressRICH5 du français PLDA est un bloc d’IP de contrôle pour la future technologie de communication série filaire PCI Express 5.0 dont la publication est attendue début 2019. Cette IP est destinée aux ingénieurs de conception pour le prototypage de puces-systèmes SoC, d'Asic et/ou de FPGA ...qui cherchent à adopter en avance de phase cette technologie dont le niveau de performance est très attendu pour les applications de pointe dans l'intelligence artificielle, l'apprentissage automatique, le stockage et la mise en réseau de masses de données, et le calcul haute performance. XpressRICH5 prend en charge la révision 0.7 de la spécification PCIe 5.0 et va permettre aux ingénieurs de tester de façon transparente les débits de liaison à 32 gigatransferts/s par voie prévus par la norme.

Le groupement d’intérêt spécifique PCI (PCI-SIG) avait révélé en juin 2017 que la prochaine évolution majeure du vénérable bus d’entrées/sorties consistait à porter sa vitesse à 32 gigatransferts par seconde par lien unidirectionnel (contre 16 GT/s pour le PCIe 4.0). L’annonce de l’organisme de standardisation avait été saluée officiellement par des sociétés comme Amphenol, Cadence, Diodes, Granite River Labs, Mellanox, Mentor, Mobiveil, Nvidia, NXP, One Stop Systems, PLDA, Synopsys et Tektronix.

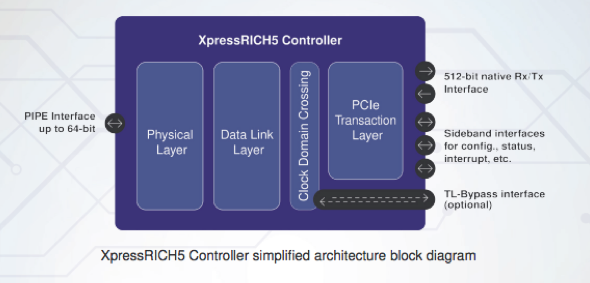

Les caractéristiques du contrôleur de bus de PLDA évolueront dans les prochains mois pour suivre au plus près les avancées des travaux de normalisation qui devraient s’achever, selon le PCI-SIG, en 2019 avec la révision 1.0. Parmi les fonctionnalités proposées par le bloc XpressRICH5 de PLDA, on notera la prise en charge de chemins de données de 512 bits requis pour la gestion confortable du débit PCIe 5.0 x16, et des services avancés de fiabilité/disponibilité/facilité de service intégrées qui assurent un déploiement sécurisé et fiable de la propriété intellectuelle dans les systèmes.

Ces fonctionnalités dites RAS (Reliability/Availability/Serviceability) incluent notamment un module d'interception d'interface PIPE, fournissant un accès en temps réel au trafic non brouillé pour faciliter le débogage, des minuteries programmables (LTSSM, ACK, NACK, et REPLAY) capables de gérer un fonctionnement sécurisé avec des appareils et des systèmes non conformes, et une fonction de mise à jour du contrôle de flux programmable, pour optimiser les performances.

Enfin, PLDA permet avec ce bloc une migration transparente du prototypage sur FPGA vers la production de circuits Asic ou SoC avec la même base de code RTL.