La société britannique LDRA, spécialiste en outils de test et de vérification de code (et qui fait désormais partie de Tasking) a présenté lors du salon Embedded World qui s’est déroulé du 11 au 13 mars 2025 à Nuremberg, une évolution de sa suite d'outils LDRA pour la prise en charge des capacités matérielles d'atténuation des effets de risques (mitigation) des architectures des processeurs Risc-V.

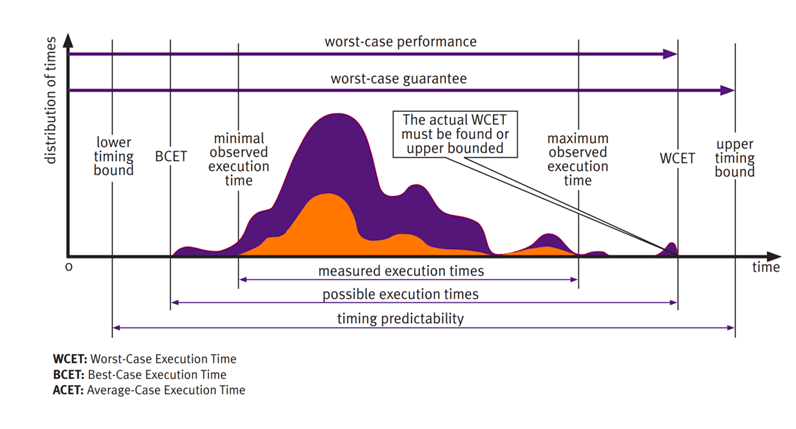

Et ce en proposant une analyse automatique de la mémoire partagée, de l'accès aux ressources de cache, des problèmes de cohérence et de mesure du "temps d'exécution au pire cas" (WECT, Worst Case Execution Time) afin de garantir un temps d'exécution déterministe sur ces processeurs RISC-V.

A travers cette technologie, les développeurs peuvent ainsi désormais, selon LDRA, accéder aux performances des systèmes multicœurs RISC-V et les optimiser, notamment en analysant l'impact des ressources partagées et de la cohérence des données sur le temps d'exécution au pire cas (WCET).

Concrètement, grâce aux outils logiciels de LDRA, les OEM peuvent automatiser l'analyse WCET et l'intégrer à un cycle de développement continu. Ce qui signifie une simplification de la conception et une augmentation de la fiabilité du code généré à travers la garantie d’une exécution déterministe dans les applications logicielles gourmandes en ressources et exigeantes en termes de sureté de fonctionnement, notamment dans les secteurs de l'avionique, de l'automobile, de l'aérospatiale, de la défense, de l'industrie, de l'énergie et du médical.

« LDRA collabore étroitement avec des fabricants de matériel afin de simplifier l'analyse des temps d'exécution des architectures multicœurs, explique Ian Hennell, directeur des opérations chez LDRA. Les entreprises qui exploitent l'architecture à jeu d'instructions RISC-V ont développé des capacités innovantes d'atténuation des risques vis-à-vis des performances multicœurs, et LDRA fournit à ce niveau les outils de développement nécessaires pour vérifier et garantir que les performances attendues répondent aux contraintes imposées par les systèmes temps réel hautes performances actuels. »

Selon LDRA, les processeurs multicœurs accélèrent les performances en exécutant le code système sur différents cœurs, avec dans de nombreux cas, sur les architectures x86 traditionnelles et Cortex-A, un partage par les cœurs des ressources telles que le cache et la mémoire. Or pour maintenir la cohérence des données, une médiation entre les cœurs pour les ressources partagées est nécessaire. Ce qui signifie qu'un cœur utilisant une ressource partagée peut involontairement “verrouiller” (lock out) d'autres cœurs ayant besoin d'accéder à la même ressource, ce qui entraîne une latence supplémentaire incertaine.

Pour les systèmes critiques qui doivent garantir l'exécution fiable et déterministe des tâches critiques, le problème est d’importance et les développeurs doivent impérativement évaluer avec précision le temps d'exécution le plus défavorable d'un système. En d’autres termes, il s’agit d’atténuer les conflits multicœurs dans les applications critiques.

Dans le cas des nouveaux processeurs RISC-V, ce derniers introduisent des fonctionnalités matérielles qui permettent d'atténuer les problèmes d'accès partagé multicœur et de cohérence des données. Par exemple, précise LDRA, les processeurs RISC-V conçus de Microchip autorisent les développeurs à allouer de la mémoire à faible latence à chaque cœur, sans aucune contention de cache partagé.

A ce niveau, la suite d'outils LDRA prend désormais en charge ces architectures RISC-V multicœurs qui gèrent la contention multicœur au niveau matériel. Et ce à travers un accès autorisés au développeurs de la suite complète d'outils LDRA, incluant l'analyse de couverture statique et structurelle, la conformité aux règles Misra et le reporting étendues, tout en tirant parti des capacités d'atténuation multicœurs du sur RISC-V.

« Évaluer les incertitudes liées à l'accès aux ressources partagées peut s'avérer complexe, et de nombreuses entreprises ont dû recourir à des services de conseil coûteux pour mesurer l'incertitude de leurs systèmes et vérifier le temps d'exécution le plus défavorable, précise Ian Hennell. Désormais, les développeurs peuvent utiliser la suite d'outils LDRA pour mesurer et analyser automatiquement l'exécution des architectures RISC-V afin de garantir avec précision et fiabilité le temps d'exécution des systèmes critiques. De plus, l'automatisation de l'analyse permet aux développeurs de réévaluer rapidement et à moindre coût les systèmes après chaque modification de code.»

LDRA précise que garantir la performance déterministe des systèmes est un processus continu, i.e chaque modification du code des systèmes centraux nécessite potentiellement une nouvelle analyse WCET afin de vérifier que les changements n'ont pas introduit de problèmes d'accès augmentant le temps d'exécution. Pour ce faire, LDRA automatise cette analyse WCET afin que les développeurs vérifient en permanence le respect des délais critiques de manière déterministe, sans avoir recours à des processus d'évaluation manuels, sujets aux erreurs, ni à des services de conseil coûteux et chronophages.

-dissolve-basic-fr.jpg)