La toute jeune entreprise américaine Rapid Silicon, dont l’ambition est de devenir un fournisseur majeur de FPGA dopés à l'intelligence artificielle (IA), bâtis sur des technologies open source et destinés à la périphérie de réseau "intelligente", entre aujourd’hui sur le marché des eFPGA (embedded FPGA). Les eFPGA, rappelons-le, sont des blocs d’IP de logique programmable que l’on peut intégrer dans une puce-système SoC ou un circuit Asic et qui offrent la flexibilité de programmation des FPGA autonomes sans le coût traditionnellement associé à ces derniers.

A l’heure actuelle, les fournisseurs d’eFPGA restent encore peu nombreux et se comptent pratiquement sur les doigts d’une seule main. Parmi ceux-ci on citera notamment le français Menta ainsi que les sociétés Achronix, Flex Logix et QuickLogic.

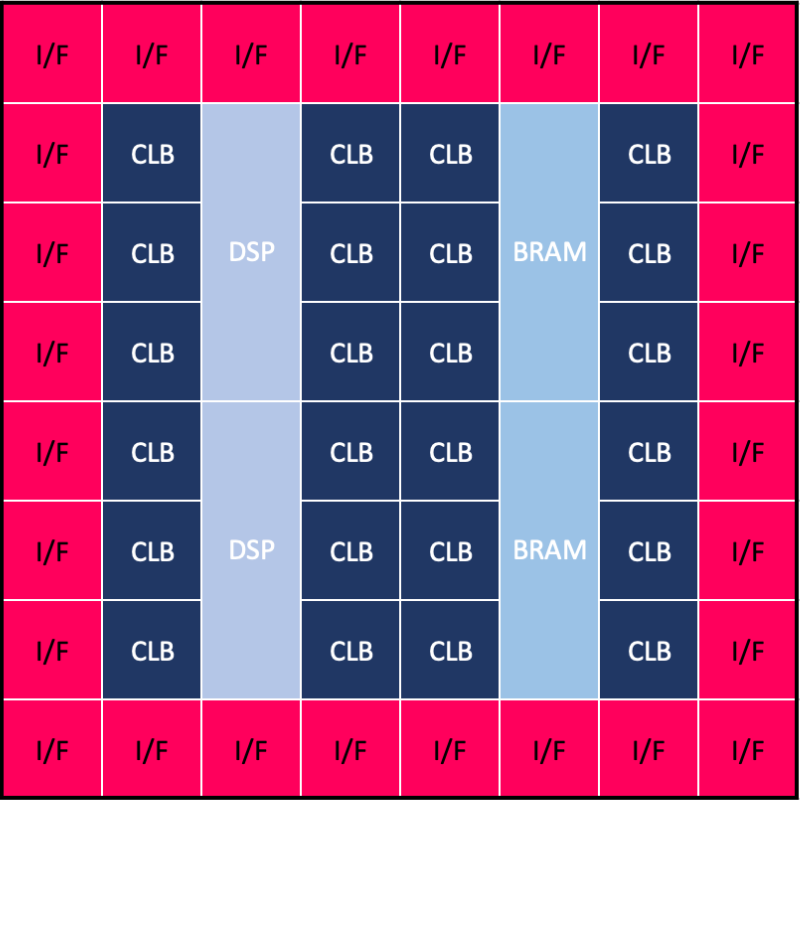

Dans le détail, l’architecture personnalisable et échelonnable de l’IP eFPGA Vega de Rapid Silicon permet d’intégrer un bloc programmable doté d’une combinaison configurable de 1,5K à 100K+ cellules logiques (CLB), tuiles BRAM (Block RAM) et DSP de type multiplieur-accumulateur (MAC). L'IP est également livrée avec des tuiles I/O pour faciliter son intégration dans une puce-système, ainsi qu’avec un bloc logique simplifiant sa configuration.

Dans le détail, l’architecture personnalisable et échelonnable de l’IP eFPGA Vega de Rapid Silicon permet d’intégrer un bloc programmable doté d’une combinaison configurable de 1,5K à 100K+ cellules logiques (CLB), tuiles BRAM (Block RAM) et DSP de type multiplieur-accumulateur (MAC). L'IP est également livrée avec des tuiles I/O pour faciliter son intégration dans une puce-système, ainsi qu’avec un bloc logique simplifiant sa configuration.

Selon Rapid Silicon, l’eFPGA Vega, qui repose sur des cellules standard, est en outre portable sur différents nœuds technologiques auprès de différentes fonderies.

Disponible pour l’heure pour évaluation et sous accord de confidentialité, l’IP eFPGA Vega est fournie avec la chaîne d’outils open source Raptor Design Suite pour FPGA qui couvre les phases de simulation, de synthèse, de placement/routage et de génération et de configuration de bitstreams. Intégrable au sein du framework open source Migen+LiteX pour la gestion d’IP lors de la mise au point de puces-systèmes, la suite de conception de Rapid Silicon est également livrée avec Rapid Power Estimator pour l'estimation de la consommation du bloc eFPGA et avec le plug-in RapidGPT pour VSCode conçu pour améliorer le processus de conception FPGA et augmenter la productivité des concepteurs hardware.

-dissolve-basic-fr.jpg)