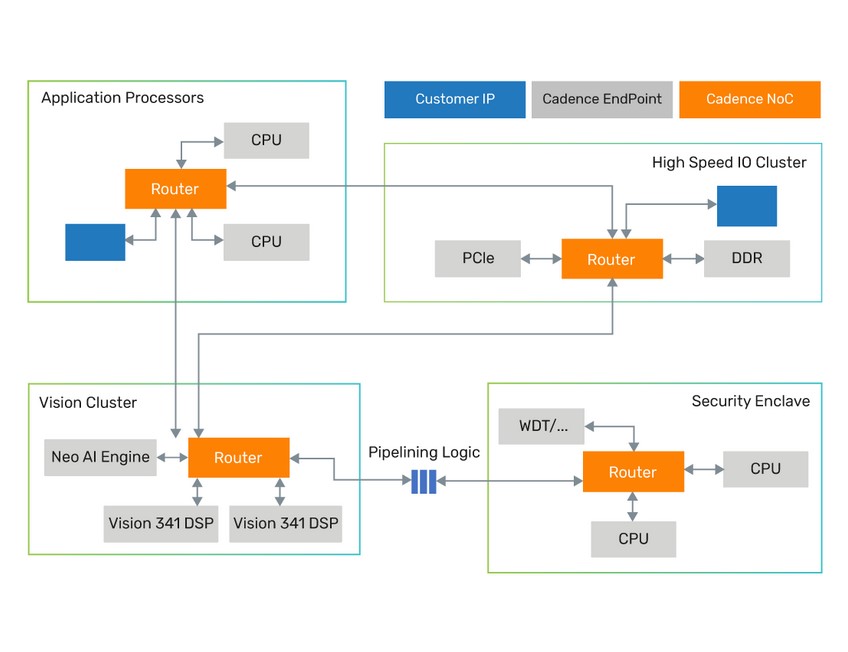

Bien ancrée sur le créneau des technologies de réseau-sur-puce NoC (Network-on-Chip), la société Arteris, basée aux Etats-Unis mais d’origine française, a désormais un concurrent de poids. L’américain Cadence Design Systems élargit aujourd'hui son portefeuille de blocs d’IP système avec un NoC dénommé Janus. (Janus est le dieu romain du passage et des portes…). Cette IP, selon Cadence, est censée gérer de manière efficace les communications à haute vitesse au sein et entre circuits intégrés complexes avec une latence minimale, tout en permettant aux utilisateurs d’atteindre rapidement, et avec un risque réduit, leurs objectifs de consommation, de performances et de surface silicium (PPA, Power, Performance and Area).

L’IP NoC Janus exploite l'héritage de Cadence en matière d'outils de génération RTL Tensilica. Les utilisateurs peuvent ainsi tirer parti de la gamme de logiciels et de ressources matérielles de l’Américain pour la simulation et l'émulation de leur réseau-sur-puce et obtenir des informations détaillées sur ses performances à l'aide de l'outil d'analyse des performances système (SPA) de Cadence. Cette capacité d’exploration architecturale permettrait de concevoir le NoC le plus approprié aux besoins du produit résultant.

Si l’on en croit la société, le NoC Janus atténue les problèmes de congestion en matière de routage et de timing associés aux interconnexions SoC complexes d’aujourd’hui, problèmes qui n’apparaissent souvent qu’après la mise en œuvre physique.

Répondant aux besoins les plus immédiats, le NoC de première génération de Cadence prend en charge les mémoires standard de l'industrie ainsi que les protocoles de cohérence d’interfaces d’entrées/sorties les plus répandus (AXI4, AHB…). Le NoC Janus, dont la disponibilité est attendue courant juillet, se caractérise aussi par une architecture échelonnable, les utilisateurs pouvant concevoir un sous-système et le réutiliser dans le contexte d’une puce-système SoC complète et, à plus long terme, dans le contexte d’un système multipuce.