Le spécialiste des blocs de compression vidéo et de cryptage pour Asic et FPGA Barco Silex a étoffé son portefeuille d’IP de sécurité avec des fonctions de hachage SHA-3. Les algorithmes de hachage, rappelons-le, sont utilisés pour vérifier l’intégrité des messages, transactions et données ...dans des applications de commerce électronique, d’archivage et de communication. Ils transforment ces messages en une empreinte numérique (message digest) unique et compacte. Dès lors, la moindre modification des données originales va générer une non-concordance avec l’empreinte numérique.

Edicté par l’organisme américain Nist (National Institute of Standards and Technology) en 2012, l’algorithme SHA-3 repose sur la fonction Keccak conçue par Guido Bertoni, Joan Daemen, Michaël Peeters et Gilles Van Assche. Dans le détail, cette fonction s’appuie sur une transformation en « éponge » dans laquelle les blocs d’un message sont XORés avec des bits initiaux, puis permutés de manière réversible. Le hachage SHA-3 peut être appliqué pour protéger l’intégrité d’informations électroniques dans des applications telles que l’authentification de messages et les fonctions de signature numérique, de génération de nombres aléatoires et de dérivés de clés de cryptographie. Il n’a pas toutefois vocation à remplacer immédiatement la famille de fonctions de hachage SHA-2 qui n’ont pas encore été compromises par une attaque significative.

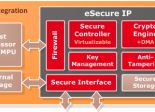

« Le hachage SHA-3 repose sur des principes de conception très différents du SHA-2 et cela en fait une excellente option de repli si ce dernier venait à être compromis, indique Sébastien Rabou, spécialiste de la sécurité chez Barco Silex. En implémentant et en proposant les algorithmes SHA-3 sous la forme d’un cœur d’IP, nous voulons assurer à nos clients qu’ils peuvent bâtir des produits dont la sécurité est vraiment pérenne. » Fourni avec des pilotes logiciels destinés à faciliter son intégration dans des composants, le bloc d’IP BA418 de la firme belge est aujourd’hui disponible pour les utilisateurs d’Asic et de FPGA.

-dissolve-basic-fr.jpg)