Toshiba peaufine actuellement un bloc matériel d'accélération de réseaux de neurones profonds (DNN, Deep Neural Network) qui vise à améliorer les fonctions de reconnaissance d’image des systèmes d’aide évoluée à la conduite automobile (ADAS) et des équipements de conduite autonome. ...Le Japonais compte combiner cette IP avec des technologies traditionnelles de traitement d’image au sein d’une même puce-système et échantillonner à partir de septembre 2019 un processeur ad hoc de reconnaissance d’images sous le petit nom de Visconti 5.

Selon Toshiba, le bloc d’IP DNN s’appuie sur l’apprentissage profond pour assurer la détection et l'identification d’un large éventail d’objets avec une précision plus grande que ce que permet aujourd’hui la reconnaissance d’images reposant sur des techniques d’apprentissage automatique et de reconnaissance de motifs conventionnelles. L’idée étant que le SoC Visconti 5 puisse reconnaître des panneaux de signalisation et des conditions routières lorsque le véhicule se déplace à grande vitesse et ce avec une consommation électrique limitée.

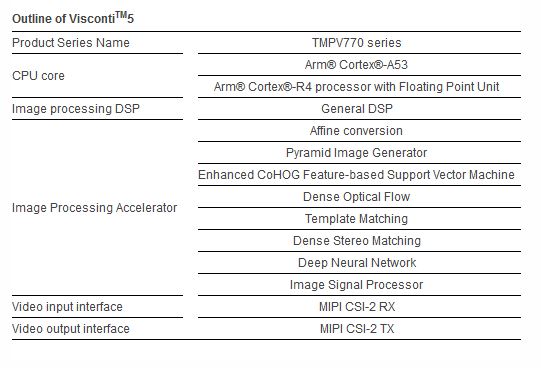

Dans le détail, les futures puces-systèmes Visconti 5 seront architecturées autour d’un cœur Arm Cortex-A53 et d’un cœur temps réel Arm Cortex-R4 avec unité de calcul en virgule flottante, d’un DSP générique de traitement d’image et d’un accélérateur de traitement d’image intégrant notamment un module ISP (Image Signal Processor) et le bloc DNN. Ses interfaces d’entrées/sorties vidéo seront compatibles avec la spécification Mipi CSI-2.