Synopsys affirme être la première société à proposer un ensemble complet de blocs d’IP pour la technologie PCI Express 6.0 dont le contrôleur, la couche physique (PHY) et l’IP de vérification. Une offre qui ouvre la voie au développement de puces-systèmes (SoC) compatibles ...avec ce standard dont la publication officielle est attendue d’ici à la fin de l’année.

Le PCIe 6.0 va porter la vitesse du vénérable bus d’entrées/sorties à 64 gigatransferts par seconde par lien unidirectionnel (contre 32 GT/s pour le PCIe 5.0) tout en maintenant des caractéristiques de basse consommation et la rétrocompatibilité avec les générations précédentes. Ce qui devrait permettre de transférer un débit maximal de 256 Go/s dans une configuration à 16 liens (x16).

Selon Synopsys, la solution DesignWare IP PCIe 6.0 prend en charge les dernières fonctionnalités de la spécification, notamment la modulation d’impulsions en amplitude à quatre niveaux PAM-4 (Pulse Amplitude Modulation – 4 Levels) à 64 GT/s, le mode d’encodage FLIT (Flow Control Unit), pour assurer un mécanisme de correction d’erreurs à faible latence et haute efficacité, ainsi que le mode de consommation L0p (Low power State) qui permet d’étager la consommation d’énergie en fonction de la bande passante utilisée sans interruption du trafic.

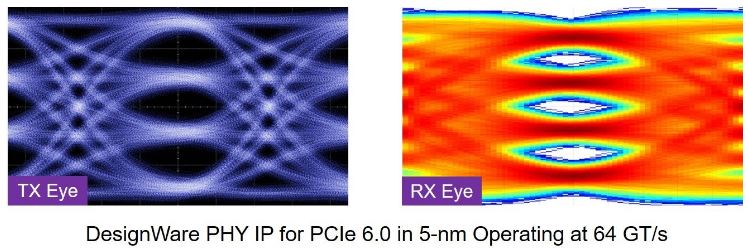

Dans le détail le contrôleur PCIe 6.0, qui se déploie sur une architecture 1 024 bits, est censé s’accommoder d’une bande passante de 64 GT/s x16 tout en répondant aux contraintes de timing à 1 GHz. Le bloc d’IP PHY, quant à lui, fournit des algorithmes DSP qui optimisent l’égalisation analogique et numérique afin de maximiser l’éco-efficacité quel que soit le canal de transmission. Son architecture permet une intégration dense des liens x16 au sein d’une puce-système, tandis que le chemin de données garantit une latence ultrafaible, assure Synopsys.

« Les applications avancées de cloud computing, de stockage et d'apprentissage automatique impliquent des transferts d'importantes quantités de données, ce qui oblige les concepteurs à intégrer les dernières interfaces à haut débit en date avec une latence minimale pour répondre aux besoins en bande passante de ces systèmes », précise John Koeter, senior vice-président senior marketing et stratégie pour les IP de Synopsys. Les IP contrôleur et PHY PCIe 6.0 de la société seront disponibles en accès anticipé dans le courant du troisième trimestre, l’IP de vérification étant d’ores et déjà disponible.