Quelques mois après la publication de la spécification PCI Express 5.0, la société américaine Rambus, spécialiste des blocs d’IP et des puces d’accélération et de sécurisation des données, annonce la disponibilité d’une solution complète d’interface conforme ...à ce standard qui pousse la vitesse du vénérable bus d’entrées/sorties à 32 gigatransferts par seconde (contre 16 GT/s pour le PCIe 4.0).

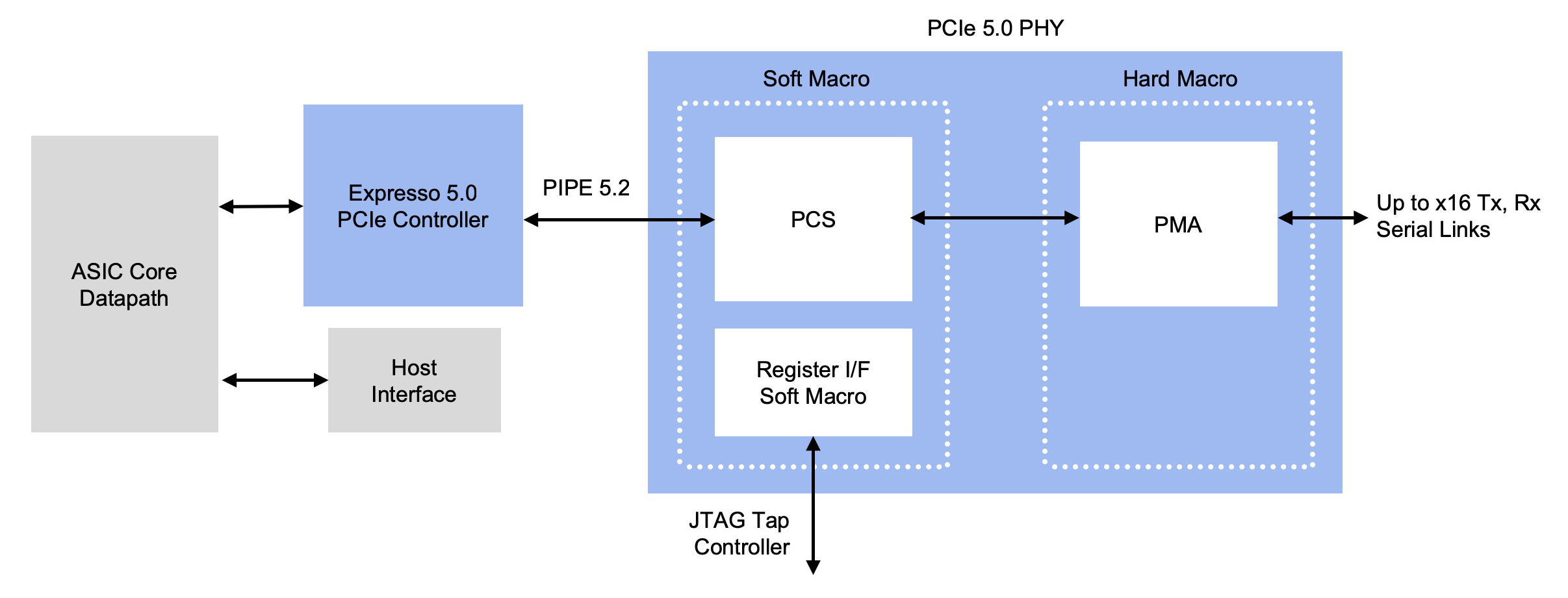

Destinée aux concepteurs de puces-systèmes SoC, l’offre de Rambus, rétrocompatible avec les technologies PCIe 4.0, 3.0 et 2.0, comprend à la fois un bloc de couche physique (PHY) et un contrôleur numérique. Selon l’Américain, le bloc PHY est conçu pour un procédé de gravure FinFET avancé en 7 nm et la solution intégrée offre des niveaux très élevés de consommation, de performances et d’empreinte silicium.

Pour rappel, la spécification PCI Express 5.0 vise à satisfaire les besoins à venir d’applications à hautes performances comme l’intelligence artificielle, l’apprentissage automatique, les jeux, la vision artificielle, le stockage et les équipements réseau.

A noter que la solution PCIe 5.0 de Rambus intègre un cœur de contrôleur numérique hautes performances issu de la récente acquisition de la société Northwest Logic (lire notre article ici).

Le contrôleur et le bloc PHY (qui s’accommode de liaisons PCIe 5.0 x16 pour un débit cumulé de 128 Go/s) sont proposés sous forme d’une solution entièrement validée et intégrée, mais ils peuvent aussi être commercialisés sous licence séparément et utilisés avec des IP tierces.

La prise en charge de la technologie Compute Express Link (CXL) est également assurée pour la connexion entre un processeur hôte et des accélérateurs de traitement spécifiques dans le cas d’architectures de calcul hétérogènes.