L’américain Microchip a dévoilé un programme spécifique, le Early Access Program (EAP), qui vise à donner accès, en avance de phase, à une prochaine famille de puces-systèmes FPGA PolarFire dotées "en dur" d'un sous-système processeur temps réel compatible Linux fondé sur des cœurs RISC-V.... Cette annonce a été faite à l'occasion du RISC-V Summit qui se tient du 10 au 12 décembre à San Jose en Californie. Les clients EAP qualifiés pourront ainsi commencer à concevoir dès maintenant une solution exploitable fondée sur cette approche,et ce grâce à l’environnement pour FPGA Libero SoC 12.3 et à l'environnement de développement logiciel SoftConsole 6.2 de Microchip . Avec pour le débogage, l’appui du modèle virtuel du sous-système processeur baptisé Renode (issu de la société Antmicro).

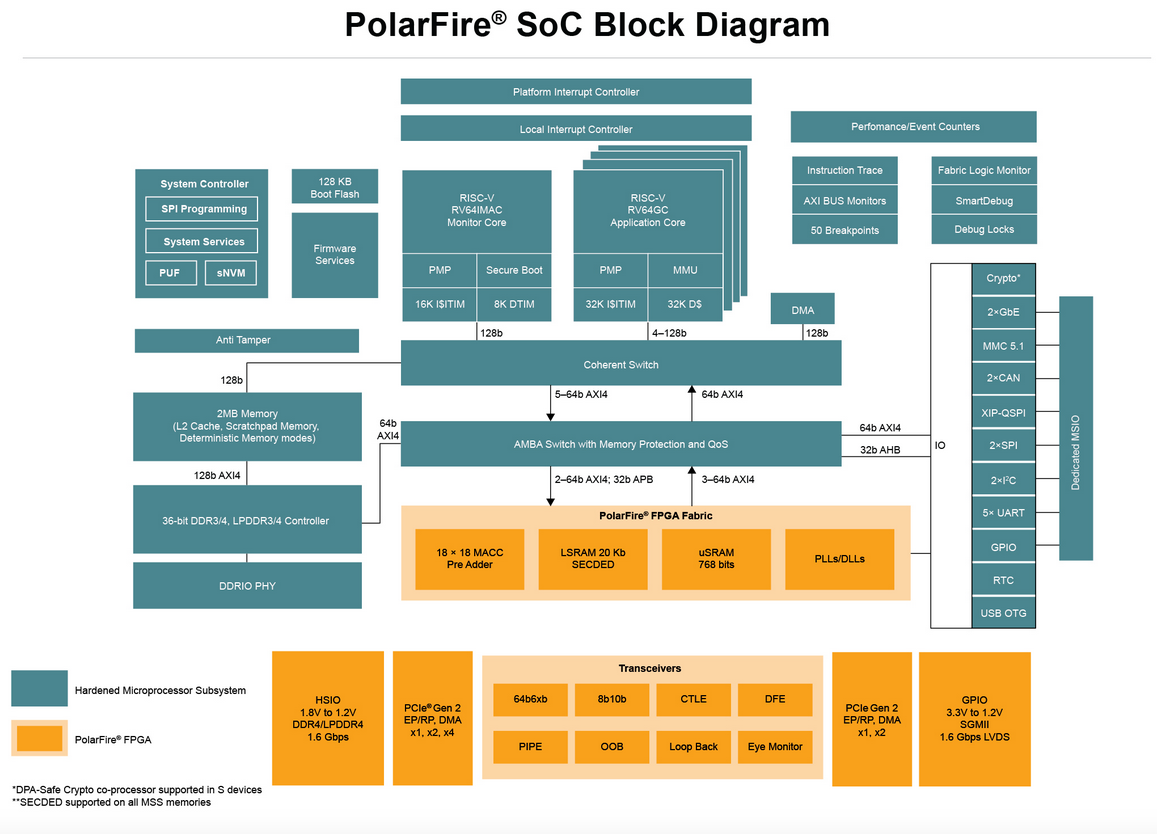

Dés la fin de l’année 2018, Microchip avait dévoilé ses intentions vis-à-vis de la technplogie RISC-V avec la description d’une architecture associant les FPGA PolarFire de milieu de gamme et un sous-système processeur complet, reposant sur le jeu d'instructions ouvert et libre de droits RISC-V. Cette architecture PolarFire + RISC-V apporte aux concepteurs qui mettent au point des applications sous Linux des capacités de multitraitement asymétrique (AMP) déterministe en temps réel, fondé sur plusieurs cœurs de processeur (jusqu'à quatre). Développée en collaboration avec la société SiFive, spécialiste des coeurs de processeur RISC-V, cette approche intègre aussi un sous-système mémoire L2 de 2 Mo, configuré en tant que mémoire cache, mémoire bloc-notes ou mémoire d’accès direct (voir schéma ci-dessous)

La future famille de SoC FPGA PolarFire de Microchip équipés "en dur" de grappes de coeurs RISC-V cohérentes et d'une mémoire L2 déterministe pourra prendre en charge simultanément des applications temps réel et des systèmes d'exploitation riches de type Linux avec une efficacité énergétique élevée. Et ce pour la mise au point de passerelles et de périphériques à forte capacité de calcul exigeant en parallèle des fonctions de contrôle déterministe sur les marchés des systèmes de communication, de la Défense, de l’automatisation industrielle et du médical. Le premier membre de cette famille SoC FPGA, référencé MPFS250T, devrait être échantillonné au cours du troisième trimestre 2020.

Pour faciliter le travail des concepteurs, les SoC PolarFire à coeurs RISC-V intégreront des capacités de débogage étendues, comme notamment la trace d'instructions et les moniteurs de bus AXI (Advanced eXtensible Interface) configurables issus de la société UltraSoC, 50 points d'arrêt, des moniteurs FPGA et l'analyseur logique à deux canaux SmartDebug de Microchip. L'architecture SoC PolarFire comprend en outre des fonctionnalités de fiabilité et de sécurité telles que la correction d'erreur simple et la détection d'erreur double (SEC-DED) sur toutes les mémoires, la protection de la mémoire physique, un noyau cryptographique résistant aux attaques DPA (Differential Power Analysis), un démarrage sécurisé de qualité militaire et 128 Ko de mémoire flash de démarrage.

Actuellement les partenaires de l'écosystème RISC-V Mi-V de Microchip qui se disent prêts à prendre en charge le SoC PolarFire d’un point de vue logiciel incluent les sociétés Wind River (avec VxWorks, voir notre article ici), Mentor Graphics (Nucleus), wolfSSL, Express Logic, Veridify, Hex Five et FreeRTOS (Amazon) ainsi que les éditeurs d'outils de développement IAR et AdaCore.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)