Lors du salon Embedded World 2023 qui s’est tenu mi-mars, la jeune société allemande MachineWare (*), créée en 2022 et basée à Aix-la-Chapelle, a montré pour la première fois son outil SIM-V, un simulateur de jeu d'instructions RISC-V ultrarapide pour une puce en cours de conception et réalisé avec le langage de haut niveau SystemC TLM (Transaction-level Modeling). Une technologie destinée au développement et à la vérification précoces de logiciels embarqués sur RISC-V.

SIM-V combine des performances de simulation de haut niveau avec la possibilité de personnaliser le simulateur pour des applications allant des plus petits appareils embarqués à de gros calculateurs déployés sur le terrain en périphérie de réseau (edge).

Dans un écosystème RISC-V extrêmement dynamique, MachineWare note que d'énormes quantités de logiciels sont désormais développées ou portées vers ces cibles. Or la vérification de la fonctionnalité correcte des nouvelles piles logicielles est d'une importance primordiale pour mettre sur le marché des produits sans bogues, fondés sur une architecture RISC-V.

Concrètement, MachineWare permet aux développeurs de logiciels de tester en temps réel des piles logicielles complètes, y compris le micrologiciel de la puce, le noyau du système d'exploitation et les applications de l'espace utilisateur, telles que les machines virtuelles Java ou les environnements graphiques. SIM-V répond ainsi au besoin de plates-formes virtuelles SystemC RISC-V hautes performances dans des secteurs tels que l'électronique automobile, l'intelligence artificielle et les télécommunications.

Concrètement, MachineWare permet aux développeurs de logiciels de tester en temps réel des piles logicielles complètes, y compris le micrologiciel de la puce, le noyau du système d'exploitation et les applications de l'espace utilisateur, telles que les machines virtuelles Java ou les environnements graphiques. SIM-V répond ainsi au besoin de plates-formes virtuelles SystemC RISC-V hautes performances dans des secteurs tels que l'électronique automobile, l'intelligence artificielle et les télécommunications.

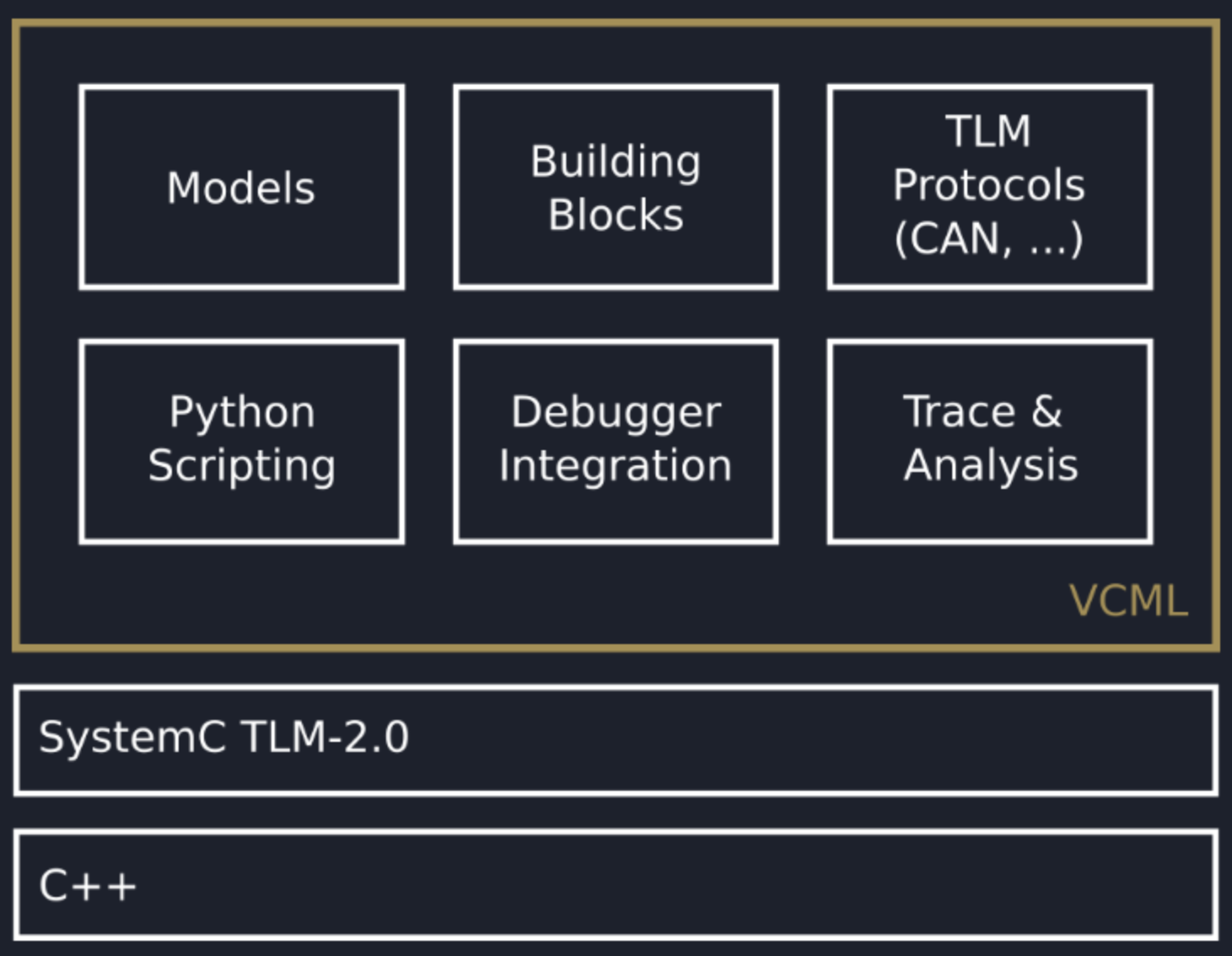

La technologie de MachineWare s’appuie sur un moteur de compilation de type Just-In-Time FTL (Fast Translator Library) et sur la bibliothèque open source VCML (Virtual Components Modeling Library) de la société, qui autorisent des performances de simulation élevées, surpassant de plus de deux fois, selon la société, les vitesses enregistrées en utilisant le simulateur open source QEMU, très utilisé par les développeurs.

Au-delà, MachineWare souligne que SIM-V prend en charge les scénarios d'intégration continue, là où les plates-formes virtuelles traditionnelles sont souvent lancées pour une seule exécution quotidienne, ce qui rend difficile le suivi des changements exacts introduits par un comportement défectueux. Avec SIM-V, de grandes piles logicielles peuvent être ainsi être mises en place et vérifiées bien avant que les premiers prototypes physiques ne soient disponibles.

Lors d’Embedded World 2023, MachineWare a notamment fait la démonstration de sa plate-forme virtuelle sur RISC-V avec la prise en charge complète de l’environnement Android 12. Selon MachineWare, le démarrage d'une image Android standard non modifiée nécessite l'exécution de plus de 100 milliards d'instructions, d’où la nécessité impérieuse de passer par un simulateur virtuel pour la vérification et le débogage logiciel en avance de phase.

(*) MachineWare est une émanation de l’Institute for Communication Technologies and Embedded Systems de l’université RWTH (Rheinisch-Westphalian Technical University) d’Aix-la-Chapelle.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-dissolve-basic-fr.jpg)