Destiné aux concepteurs de cœurs de processeur RISC-V, la bibliothèque en open source de couverture fonctionnelle de code SystemVerilog RISC-V du britannique Imperas fournit un accès complet à un fichier source pour la vérification avancée d’une microarchitecture RISC-V.

Cette bibliothèque de couverture fonctionnelle, une première sur le marché selon Imperas, est destinée dans sa version initiale aux versions RV32IMC et RV64 du jeu d'instructions RISC-V. D’autres extensions ratifiées sont en cours de développement et seront publiées dans le cadre de l’outil de simulation de jeux d’instruction riscvOVPsimPlus d’Imperas qui s’appuie sur les modèles de référence de la société avec une licence gratuite qui couvre une utilisation commerciale et académique.

Pour rappel, les équipes de vérification d'une conception utilisent l'analyse de la couverture comme mesure clé de la progression vers l'achèvement d’un plan de vérification complet. Au sein d’une conception complexe telle qu'un processeur RISC-V, les instructions ISA (Instruction Set Architecture) fournissent les directives de base pour concevoir les fonctionnalités des instructions. A ce niveau, le développement d'une bibliothèque de couverture fonctionnelle SystemVerilog à l’échelon 'instruction" nécessite, selon Imperas, à la fois une compréhension du processus de vérification et les exigences générales de la communauté des ingénieurs de vérification.

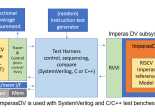

Dans ce cadre, la société avait déjà développé ce type de bibliothèques au fil du temps pour prendre en charge plusieurs projets utilisateur à travers son outil commercial ImperasDV (voir notre article). Cependant, avec la croissance rapide de l'adoption du RISC-V, Imperas estime que la communauté émergente d’équipes de vérification de design de RISC-V a désormais un besoin urgent en IP de vérification de qualité provenant d'une source fiable.

Parallèlement, SystemVerilog et UVM sont devenus au fil du temps les normes les plus fiables en matière de vérification de puces-systèmes SoC et de blocs d’IP. SystemVerilog a été adopté comme norme par l'IEEE et l’organisme Accellera sur la base du langage Superlog développé à l'origine par la société Co-Design Automation dans laquelle Simon Davidmann, l’actuel CEO d’Imperas, travaillait.

« La couverture fonctionnelle est fondamentale pour tous les plans de vérification des processeurs modernes car il marque la progression vers l'achèvement du projet et la sortie vers la fabrication de prototypes, commente Allen Baum d'Esperanto Technologies et président du groupe d'experts (SIG) Architecture Test de l'organisme RISC-V International. La publication de la bibliothèque de couverture fonctionnelle Imperas SystemVerilog avec une licence gratuite permissive bénéficiera désormais à toutes les équipes de vérification RISC-V et complètera le travail du SIG Architecture Test. »

Le paquet logiciel gratuit riscvOVPsimPlus, comprenant le modèle de référence RISC-V d’Imperas, les dernières suites de tests et l'analyse de la couverture des instructions, y compris les mises à jour des dernières spécifications ratifiées par l'organisme RISC-V International, est désormais disponible sur le site Open Virtual Platforms (OVPworld).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-dissolve-basic-fr.jpg)