Soutenu par un financement de l'EuroHPC JU (Joint Undertaking), le projet DARE (Digital Autonomy with RISC-V in Europe) vient d’être lancé en vue de développer du matériel et des logiciels fondés sur des architectures ouvertes RISC-V qui alimenteront de futurs calculateurs haute performance européens dits exascale.

Le projet, financé à hauteur de 240 millions d'euros, débutera par la conception et le développement d'un processeur et de deux accélérateurs RISC-V. Il comprendra donc un accélérateur vectoriel (VEC) pour le calcul de haute performance (High Performance Computer) et les applications émergentes liées à la convergence entre ce type de calculateur et l’intelligence artificielle (IA); une unité de traitement conçue pour l'accélération de l'inférence d'IA dans les applications de calcul haute performance; et un processeur à usage général optimisé pour les charges de travail d’un supercalculateur.

Selon les promoteurs du projet DARE, cette initiative permettra à l'Europe de développer des technologies HPC souveraines, favorisant un écosystème européen autonome, et apportant une alternative économe en énergie par rapport aux autres architectures de microprocesseurs.

S'appuyant sur les recherches des projets déjà financés par l'EuroHPC JU, comme l'European Processor Initiative, le MEEP (MareNostrum Experimental Exascale Platform), l’eProcessor, l’Eupilot et l’Eupex, le projet DARE fait partie de la stratégie globale de l'UE visant à atteindre l'autonomie dans les technologies matérielles stratégiques en investissant et en construisant un portefeuille technologique. A savoir des processeurs, des accélérateurs d’IA, des puces quantiques et autres composants de pointe.

DARE vise dans ce cade à construire des prototypes de systèmes HPC et d’IA fondés sur des puces électroniques standard conçues et développées par l'UE, utilisant des nœuds technologiques en silicium compétitifs. Parallèlement, le projet DARE intégrera le développement d’une pile logicielle complète pour une architecture RISC-V dédiée à un supercalculateurs intégrant de l’IA.

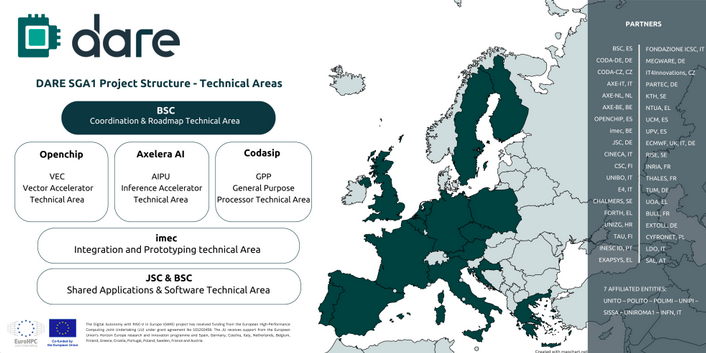

38 partenaires issus de 13 pays, dont de nombreuses PME, intègrent ce consortium qui sera coordonné par le Barcelona Supercomputing Center (BSC). Parmi les membres marquants du projet on notera la présence de l’allemand Codasip, un spécialiste du RISC-V qui travaillera sur le processeur généraliste, du néerlandais Axelera, qui s’attèlera au développement d’une unité de traitement pour l'accélération des inférences pour l’IA, et l’espagnol Openchip qui va construire une pile matérielle/logicielle pour l’accélérateur vectoriel.

Les promoteurs du projet DARE ont indiqué que les puces développées pourraient être fabriquées chez le partenaire du projet, le laboratoire belge imec sur un processus CMOS en utilisant sa ligne pilote.

Enfin, le projet DARE va utiliser une approche de co-conception matériel/logiciel en utilisant un ensemble d'applications HPC et IA européennes existantes pour guider le développement. Dans ce cadre, une pile logicielle complète, optimisée pour les chiplets, sera construite en parallèle de la conception matérielle en utilisant des technologies d’émulation et de simulation.

-dissolve-basic-fr.jpg)