La technologie de simulation de la firme britannique Imperas, spécialiste des plates-formes virtuelles pour architectures de processeurs, vient d’être mise à jour pour inclure les dernières spécifications RISC-V dont les extensions concernant la manipulation de vecteurs et de bits.... Cette spécification RISC-V dûment ratifiée est désormais disponible au sein du simulateur de plate-forme virtuelle open source RISC-V (riscvOVPsim est disponible sous licence Apache 2.0 en téléchargement sur GitHub) en tant que simulateur de jeu d'instructions (ISS) de référence pour les développeurs.

Les extensions vectorielles constituent une fonctionnalité RISC-V conçue pour répondre aux applications exigeantes telles que l'apprentissage automatique et l'algèbre linéaire pour les puces-systèmes SoC de prochaine génération.

Quant aux extensions de manipulation de bits, elles offrent aux développeurs une plus grande granularité en matière de traitement de données dans le cadre de l'architecture RISC-V, sans nécessiter d’avoir recours à un coprocesseur spécifique. La disponibilité précoce de simulateurs est donc essentielle pour l'adoption de ces extensions dans la communauté des développeurs.

Rappelons que la spécification RISC-V ISA (Instruction Set Architecture) constitue le socle de tous les développements avec RISC-V, alors que les extensions permettent de configurer un ensemble commun de fonctionnalités autour de cette architecture de base et contribuent au développement d’un écosystème large.

« L'extension vectorielle et la manipulation de bits élargiront davantage les applications des SoC à architecture RISC-V et figurent dans la feuille de route centrale des CPU d’Andes, commente Charlie Hong-Men Su, vice président exécutif et CTO d’Andes, un fournisseur de coeurs de processeur RISC-V. Nous sommes ravis de voir Imperas prendre en charge ces fonctionnalités sur les plates-formes virtuelles riscvOVPsim, ce qui va facilier le soutien aux conceptions les plus complexes des utilisateurs communs de nos deux solutions, qui utilisent les dernières spécifications et extensions RISC-V. »

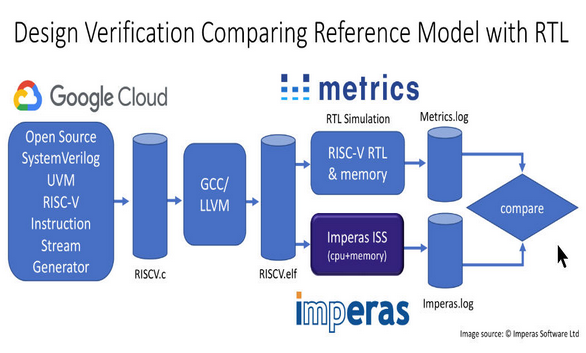

Dans le même temps, Imperas annonce une collaboration avec la société canadienne Metrics (basée à Ottawa) qui édite une plate-forme cloud pour la vérification de conceptions complexes fondées sur des FPGA, pour s'attaquer au domaine de la vérification des cœurs RISC-V. Les premières étapes de ces travaux en commun portent sur un générateur de flux d'instructions open source pour les processeurs RISC-V en s’appuyant sur les services dans le cloud de Google.

Ainsi, cette collaboration entre Imperas et Metrics va permettre aux meilleures pratiques de l’industrie pour la vérification d’être disponibles pour les cœurs RISC-V commerciaux ou open source (comme la famille CORE-V du groupe OpenHW), et ce via un accès à des référentiels de vérification conservés et maintenus. En utilisant pour ce faire les services en nuage de Google, le générateur de flux d’instructions fondé sur le langage de vérification fonctionnelle SystemVerilog UVM (Universal Verification Methodology) et la structure sur laquelle travaillent Metrics et Imperas. Les deux sociétés comptent ainsi contribuer à la création de solutions de test et de vérification “standard” pour les coeurs RISC-V (voir schéma ci-dessous).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV https://www.linkedin.com/showcase/embedded-riscv/