Favoriser l'adoption par les concepteurs de puces et les intégrateurs système de son architecture de traitement reconfigurable, tel est l’objectif affiché par la société américaine Flex Logix, connue pour sa technologie de FPGA embarqués sous forme d’IP (eFPGA) et ses moteurs d'accélération neuronale, qui compte proposer début 2023 des licences d’exploitation de sa technologie d’intelligence artificielle InferX, jusque-là mise en oeuvre uniquement dans ses propres circuits électroniques.

Ainsi, les concepteurs de puces pourront obtenir une licence leur permettant d'utiliser la technologie InferX AI sous forme de bloc d'IP. L'idée sous-jacente, au vu de l'intérêt croissant des concepteurs pour les technologies d'intelligence artificelle, est de favoriser un accès élargi aux solutions d’eFPGA de la société pour tous ceux qui veulent y adjoindre en sus un moteur d'IA.

« Alors que l'adoption commerciale des eFPGA s'accélère, avec de plus en plus d'entreprises développant des produits de qualité supérieure fondés sur la technologie de Flex Logix, nous allons aussi proposer aux concepteurs une IP d'intelligence artificielle ainsi qu'un compilateur automatisé à haute efficacité, précise Geoff Tate, cofondateur et CEO de Flex. Logix. D’ores et déjà nous avons aujourd’hui près de 40 puces sous licence utilisant notre bloc d’IP eFPGA , dont plus de 20 ont fonctionné sur silicium du premier coup. »

Dans ce domaine de la propriété intellectuelle pour semi-conducteurs, la décision de Flex Logix d'ouvrir l'accès à sa technologie InferX devrait apporter, selon la société, des performances et des avantages de coût à un plus grand nombre d'utilisateurs finaux qui vont associer eFPGA et moteur neuronal.

Pour rappel, Flex Logix permet aux utilisateurs de FPGA d'intégrer de la logique programmable dans la conception d’une puce-système, avec la prise en charge des nœuds de processus de 180 nm à 7 nm.

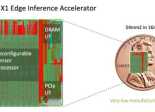

Quant à l’IP InferX, elle s’appuie sur plusieurs technologies propriétaires de Flex Logix, notamment une interconnexion à double densité que la société utilise dans ses eFPGA. Cette technologie est associée à un TPU (Tensor Processing Unit) constitué de 64 processeurs Tensor couplés avec de la mémoire SRam, et qui sont reconfigurables pour implanter des modèles de réseaux de neurones.