A l'occasion d'un événement de lancement à Munich en Allemagne, l’éditeur américain d’outils de CAO Cadence Design Systems a dévoilé une plate-forme originale de traitement des données de conception dont l’objectif est d’extraire les masses de données collectées par les outils de CAO et de les utiliser pour activer une suite d'applications de vérification utilisant des algorithmes d’intelligence artificielle (IA). Il s’agit ici, selon Cadence, d’augmenter par ce biais la couverture de fautes et d’accélérer l'analyse des causes profondes des bogues de conception détectés sur les circuits complexes de type puces-systèmes (SoC).

Ces circuits de plus en plus larges et complexes intègrent désormais des centaines de blocs d’IP qui changent constamment à mesure qu'ils évoluent. Il devient dès lors plus difficile de corréler manuellement les différents résultats et les échecs des tests, avec comme conséquence une difficulté à comprendre les causes profondes d’une panne pour laquelle des dizaines d'ingénieurs sur plusieurs semaines peuvent être mobilisés.

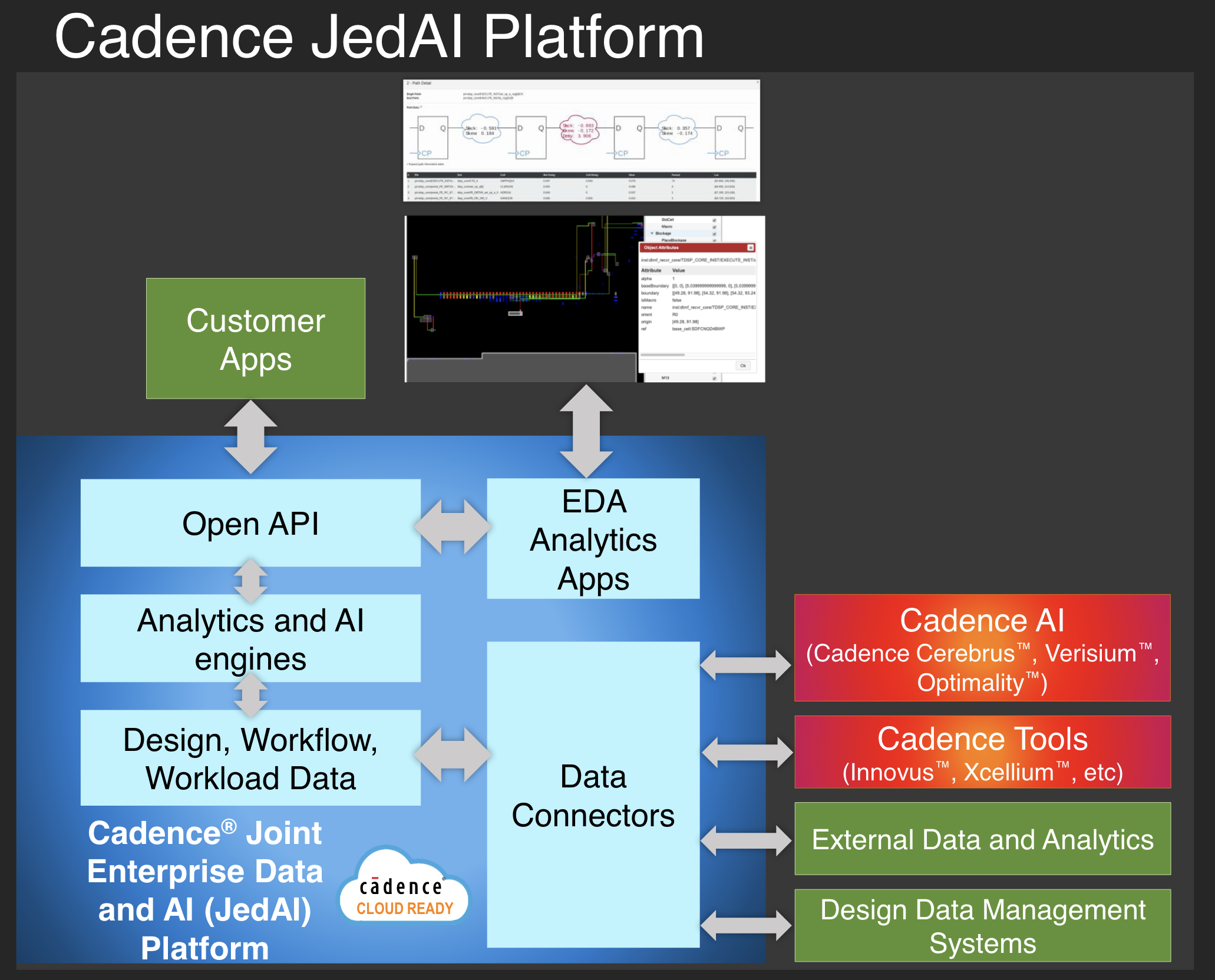

La plate-forme annoncée, baptisée JedAI (Joint enterprise data and AI) en subtile référence au film Star Wars, permet aux ingénieurs d'obtenir des informations exploitables à partir des énormes volumes de données de conception et de vérification de puces. Et par voie de conséquence d’alimenter une génération d'outils de conception et de vérification reposant sur l'IA.

Selon Cadence, cette approche est une première pierre dans un changement de l’organisation des outils de CAO actuels avec leurs algorithmes à exécution unique et à moteur unique, et leur évolution vers des algorithmes qui exploiteront les mégadonnées et l'intelligence artificielle pour optimiser de multiples exécutions de plusieurs moteurs sur l'ensemble d'un flot de conception et de vérification SoC.

La société a également annoncé sa plate-forme de vérification Cadence Verisium (*), construite sur la plate-forme JedAI, qui se présente comme une suite d'applications utilisant la capacité d'analyse de données volumineuses de JedAI pour optimiser les charges de travail de vérification. En déployant Verisium, toutes les données de vérification, y compris les formes d'onde, la couverture, les rapports et les fichiers de journalisation, sont rassemblées dans JedAI. Des modèles d'apprentissage automatique sont alors créés et d'autres métriques propriétaires sont extraites de ces données pour permettre une amélioration de la productivité de la vérification.

« Pour permettre à l'industrie des semi-conducteurs de poursuivre sa forte trajectoire de croissance, il est essentiel que le processus de conception de puces devienne plus efficace pour suivre le rythme des demandes du marché, commente Pat Moorhead, CEO et analyste en chef chez Moor Insights & Strategy. L'amélioration des processus de conception grâce à l'IA et à l'analyse de données volumineuses crée un avantage pour les équipes d'ingénierie qui peuvent désormais extraire des enseignements clés des vastes quantités de données de CAO à portée de main. »

Au-delà, Cadence note qu’auparavant, une fois qu'un projet de conception de puce était terminé, les données, souvent précieuses, étaient supprimées pour faire place au projet suivant. Or il y a des apprentissages à tirer dans les données héritées, et la plate-forme Cadence JedAI a pour ambition de permettre aux équipes d'ingénierie d'accéder à ces apprentissages et à les appliquer aux conceptions nouvelles.

Concrètement, avec la plate-forme JedAI, Cadence unifie l'analyse du Big Data et l’IA pour ses outils de vérification avec la possibilité de gérer et d’analyser des données de conception (formes d'onde, couverture dans la vérification fonctionnelle, rapports d'analyse de synchronisation/puissance/tension/variation, spécifications RTL, netlist…), des données de charge de travail (durée d'exécution, utilisation de la mémoire, métadonnées sur les entrées de chaque tâche…), ainsi que les données du flot de travail (outils et méthodologie mis en œuvre).

(*) La plateforme de vérification pilotée par l'IA Verisium fait partie du flux complet de vérification Cadence, qui comprend l'émulation avec Palladium Z2, le prototypage avec Protium X2, la simulation avec Xcelium, la vérification formelle avec Jasper et un studio virtuel et hybride avec Helium.