Avec la gamme des puces-systèmes Versal Premium Gen 2 annoncée lors du salon Electronica 2024 qui s’est déroulé du 12 au 15 novembre à Munich, le fournisseur de semi-conducteurs AMD propose les premiers SoC FPGA du marché dotés à la fois de l’interface CXL 3.1 (Compute Express Link) et d’un lien PCIe Gen6, avec en parallèle la prise en charge des mémoires LPDDR5X, le tout au sein de blocs d’IP matériels. Objectif : obtenir une connectivité rapide, un déplacement de données plus efficace et un accès à davantage de mémoire.

Pour rappel, les SoC adaptatifs Versal, issus de la société Xilinx rachetée par AMD en 2022, sont fabriqués dans un procédé 7 nm et modifiables aussi bien au niveau logiciel que matériel. Ils peuvent effectuer diverses opérations de traitement de données sur une seule plate-forme en s’appuyant sur la combinaison d’une mer de logique programmable et de plusieurs cœurs de processeurs.

Dans la puce Versal Premium Gen 2, les technologies d'interfaces et de mémoires de nouvelle génération offrent un accès rapide aux données et assurent un déplacement efficace de ces mêmes données entre processeurs et accélérateurs. Ainsi, selon AMD, les technologies CXL 3.1 et LPDDR5X permettent de débloquer rapidement des ressources mémoire pour répondre aux demandes des applications de traitement et de stockage de données en temps réel dans les centres de données, les systèmes de communication, les bancs de test et de mesure (pour l'analyse de protocoles) et les marchés de l'aérospatial et de la défense.

« Les architectes système cherchent constamment à regrouper davantage de données dans des espaces de plus en plus petits et à déplacer les données plus efficacement entre les parties du système, résume Salil Raje, vice-président senior et directeur général du groupe Adaptive & Embedded Computing chez AMD. Notre puce Versal Premium Gen 2 aide ainsi les utilisateurs à améliorer le débit global du système et l'utilisation des ressources mémoire pour atteindre de meilleures performances et débloquer des informations pour les applications les plus exigeantes installées dans le cloud ou en périphérie de réseau. »

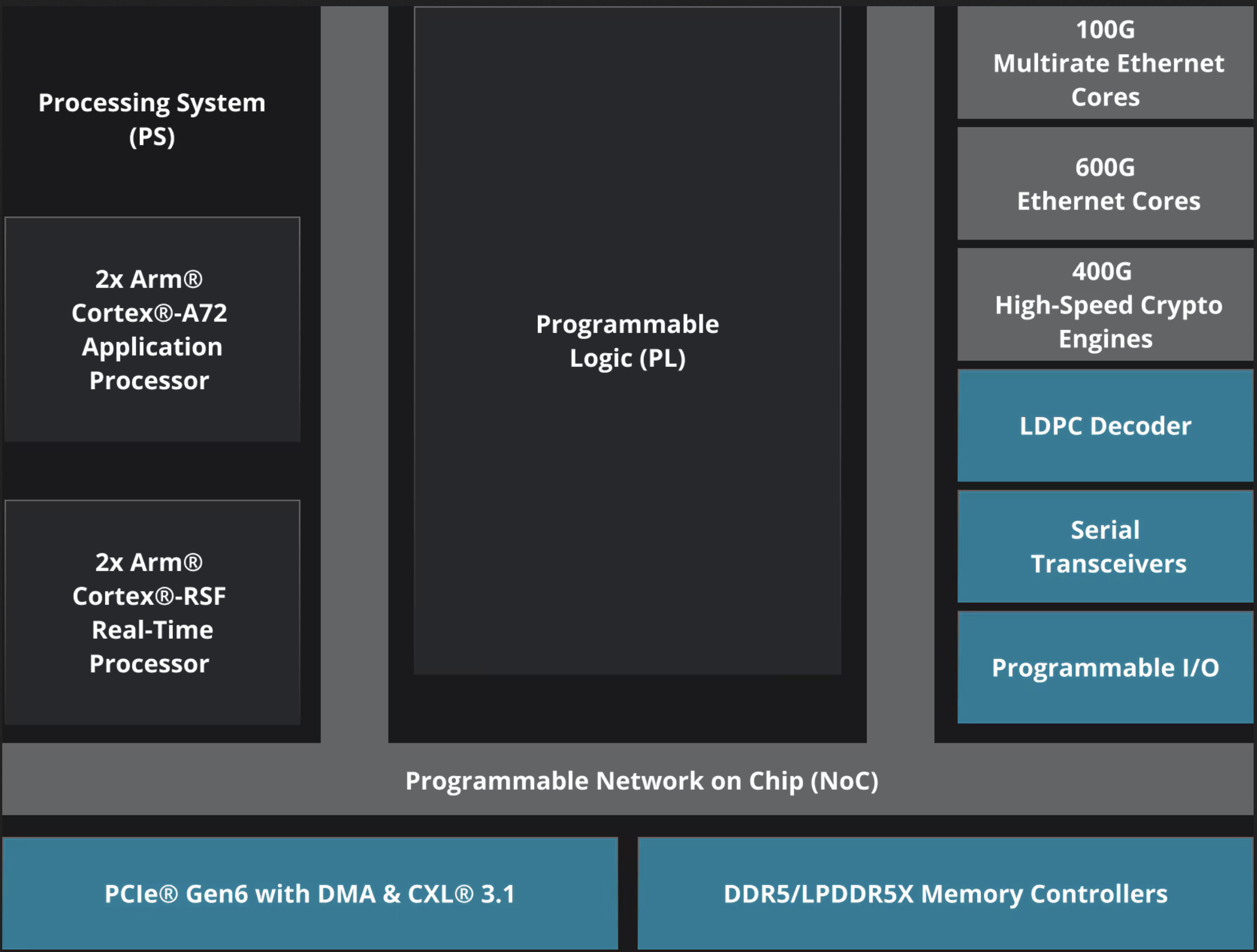

Dans le détail, le circuit offre deux cœurs Arm Cortex-A72 et deux cœurs de processeur temps réel Cortex-R5F avec, côté FPGA, jusqu’à 7 616 moteurs de calcul de type DSP, le tout relié par un réseau intégré dans la puce (NoC, Network On Chip).

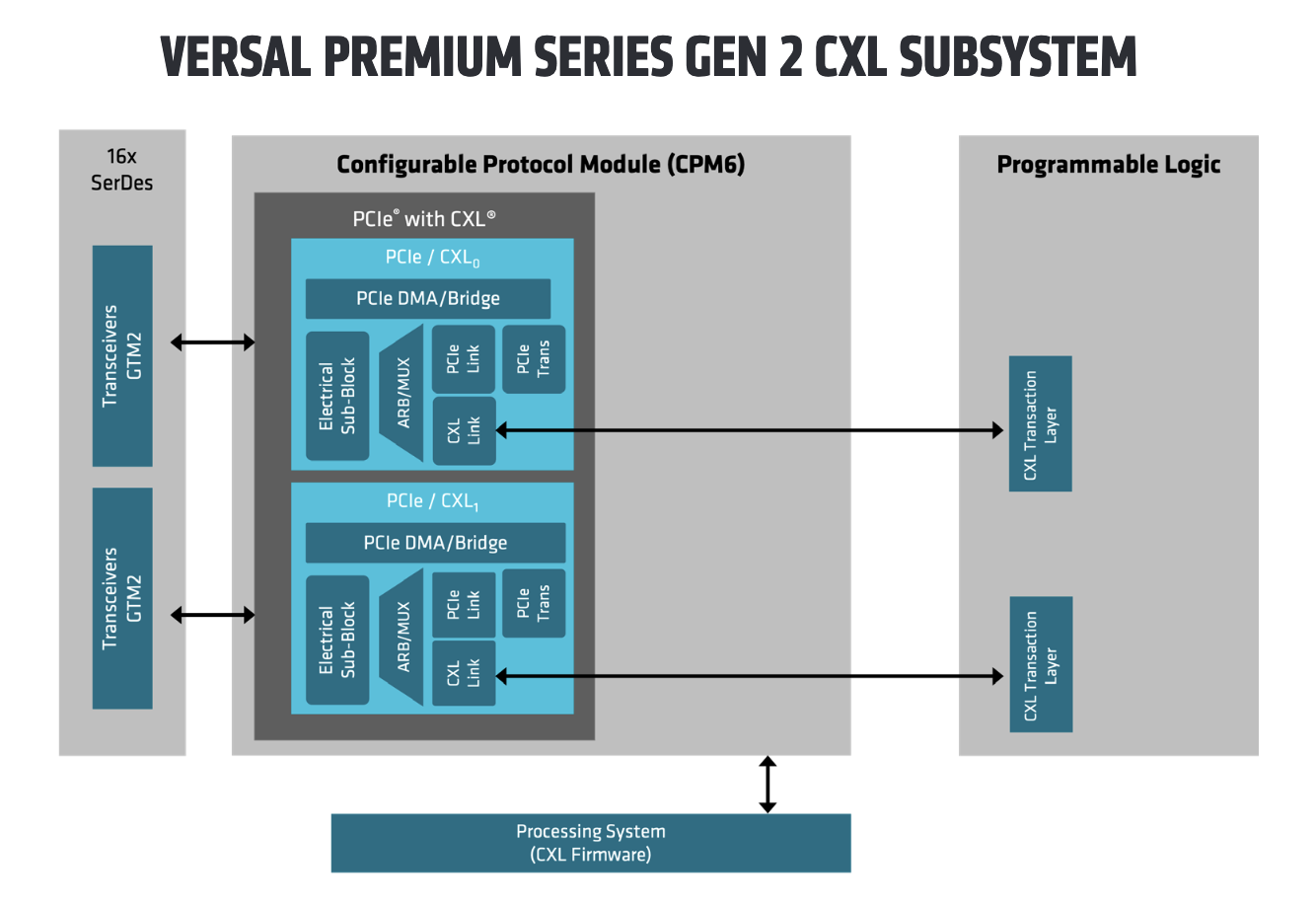

Sur ces puces, AMD défend une approche ouverte grâce à la prise en charge de la technologie CXL, une interconnexion standard de l'industrie entre processeurs et accélérateurs de type FPGA. Grâce aux technologies CXL 3.1 et PCIe Gen6, les interfaces hôtes les plus rapides du moment, les Versal Premium Gen 2 sont en mesure d'assurer une connectivité à large bande passante entre CPU hôte et accélérateur avec un débit de deux à quatre fois plus élevé que les circuits précédents d’AMD pour une bande passante doublée et des latences similaires.

Sur ces puces, AMD défend une approche ouverte grâce à la prise en charge de la technologie CXL, une interconnexion standard de l'industrie entre processeurs et accélérateurs de type FPGA. Grâce aux technologies CXL 3.1 et PCIe Gen6, les interfaces hôtes les plus rapides du moment, les Versal Premium Gen 2 sont en mesure d'assurer une connectivité à large bande passante entre CPU hôte et accélérateur avec un débit de deux à quatre fois plus élevé que les circuits précédents d’AMD pour une bande passante doublée et des latences similaires.

De plus, selon AMD, en associant le Versal Premium Series Gen 2 à un processeur Epyc de la société, les architectes système peuvent tirer parti des technologies CXL ou PCIe pour accélérer les applications gourmandes en données en apportant en sus un avantage de cohérence mémoire pour aider à gérer des calculs sur des architectures matérielles hétérogènes.

Concernant l'utilisation de la mémoire, les SoC adaptatifs Versal Premium Series Gen 2 augmentent la bande passante disponible avec une connectivité aux mémoires LPDDR5X jusqu'à 8 533 Mbit/s.