Le fournisseur de FPGA Efinix annonce la disponibilité d'une série de trois puces-systèmes SoC définies par logiciel, fondées sur des cœurs de processeur RISC-V, et spécifiquement optimisées pour la famille de FPGA Trion... Pour faciliter leur utilisation, ces SoC sont préconfigurés avec un cœur RISC-V, de la mémoire, une gamme d'E/S et ils disposent d'interfaces ouvertes pour intégrer des fonctions utilisateur. Ainsi les concepteurs peuvent notamment créer des circuits intégrés qui incluent des cœurs de calcul et accélérateurs spécifiques à architecture RISC-V au sein d’un FPGA.

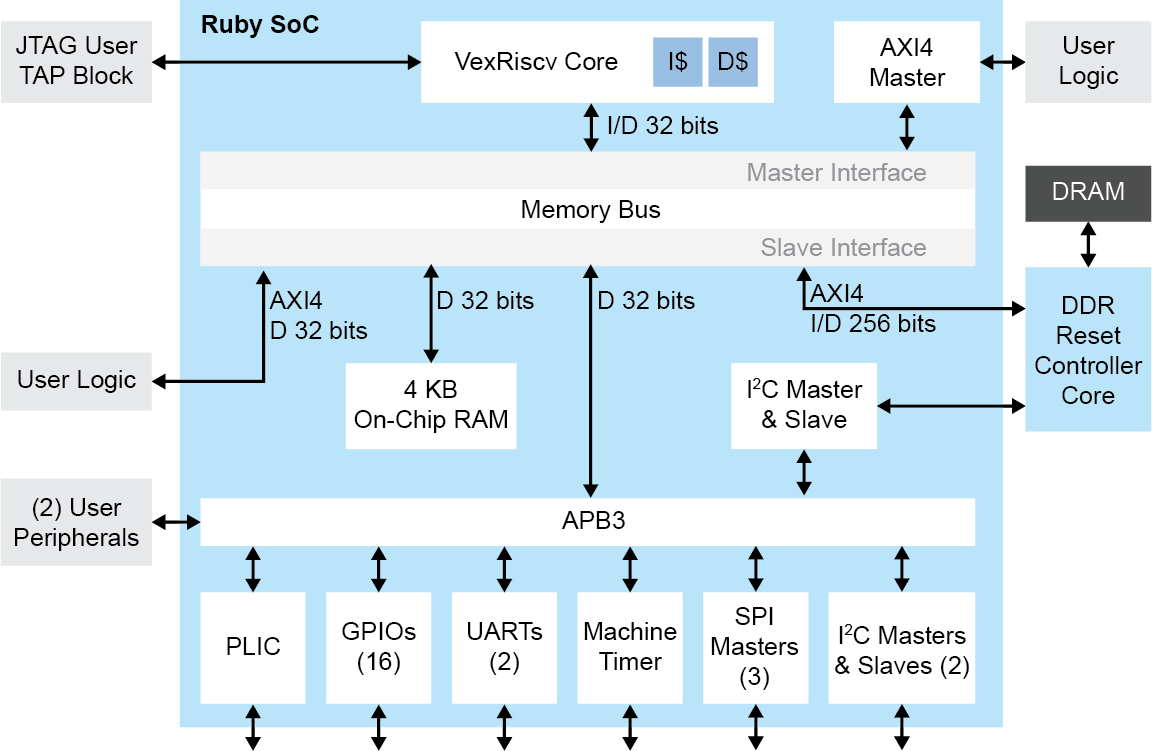

Le SoC Ruby (voir schéma ci-dessous) est un circuit haute performance doté d'une interface de contrôleur DDR DRam et destiné aux applications de contrôle/commande en temps réel et de traitement d'image. Le SoC Jade, de son côté, est un circuit polyvalent adapté aux applications qui utilisent des protocoles de communication (automatisation industrielle, enregistrement de données...). Enfin, le SoC Opal, de taile compacte et sans mémoire cache, est conçu pour les applications qui nécessitent une capacité de calcul intégrée (surveillance de systèmes, configuration et contrôle à distance...).

Ces SoC, fournis sous forme de blocs d'IP logiciels, utilisent la conception VexRiscv de Charles Papon qui a remporté le concours RISC-V Soft CPU en 2018, et qui, selon Efinix, jouit d’une popularité grandissante au sein de la communauté open source, grâce notamment à la prise en charge de Linux. Le cœur VexRiscv, disponible sur GitHub, est fourni sous la forme d’un code écrit en SpinalHDL, une version de haut niveau du langage de programmation HDL.

Rappelons que les FPGA d’Efinix reposent sur une structure originale fondée sur des cellules à tables de correspondance LUT (Look-Up-Table) dans lesquelles les éléments logiques peuvent fonctionner soit comme des tables LUT traditionnelles, soit comme une grille de routage. Selon Efinix, cette approche apporte des gains en performances énergétiques, en puissance de calcul ainsi qu'en surface de silicium (à performance équivalente) d'un facteur 4.

Sur les circuits d'Efinix déjà réalisés avec un procédé de gravure en 40 nm, des vitesses d'horloge à plus de 200 MHz ont ainsi été atteintes sans difficultés.

Les conceptions à cœur RISC-V seront intégrés, selon les besoins, dans l'un ou l'autre des FPGA de la société, offrant de 4 à 150 000 éléments logiques LE avec plus de 8 Mo de mémoire RAM et jusqu'à 500 multiplicateurs.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-blocks-basic-fr.jpg)