La société américaine Wave Computing, qui a repris mi-2018 Mips Technologies, met dans le domaine open source les cœurs Mips32 microAptiv dans le cadre de la mise à jour des composants du programme Mips Open. ...Dans la pratique les participants au programme Mips Open ont accès sans restrictions et gratuitement (sans frais de licence ou redevances donc) à la dernière version en date des architectures Mips 32 bits et 64 bits. Les utilisateurs peuvent ainsi télécharger les jeux d’instructions (ISA) ad hoc y compris un certain nombre d’extensions telles que celles liées à la virtualisation, au multithreading, au traitement SIMD (Single Instruction Multiple Data), aux fonctions DSP et à la compression de code microMips (lire notre article ici).

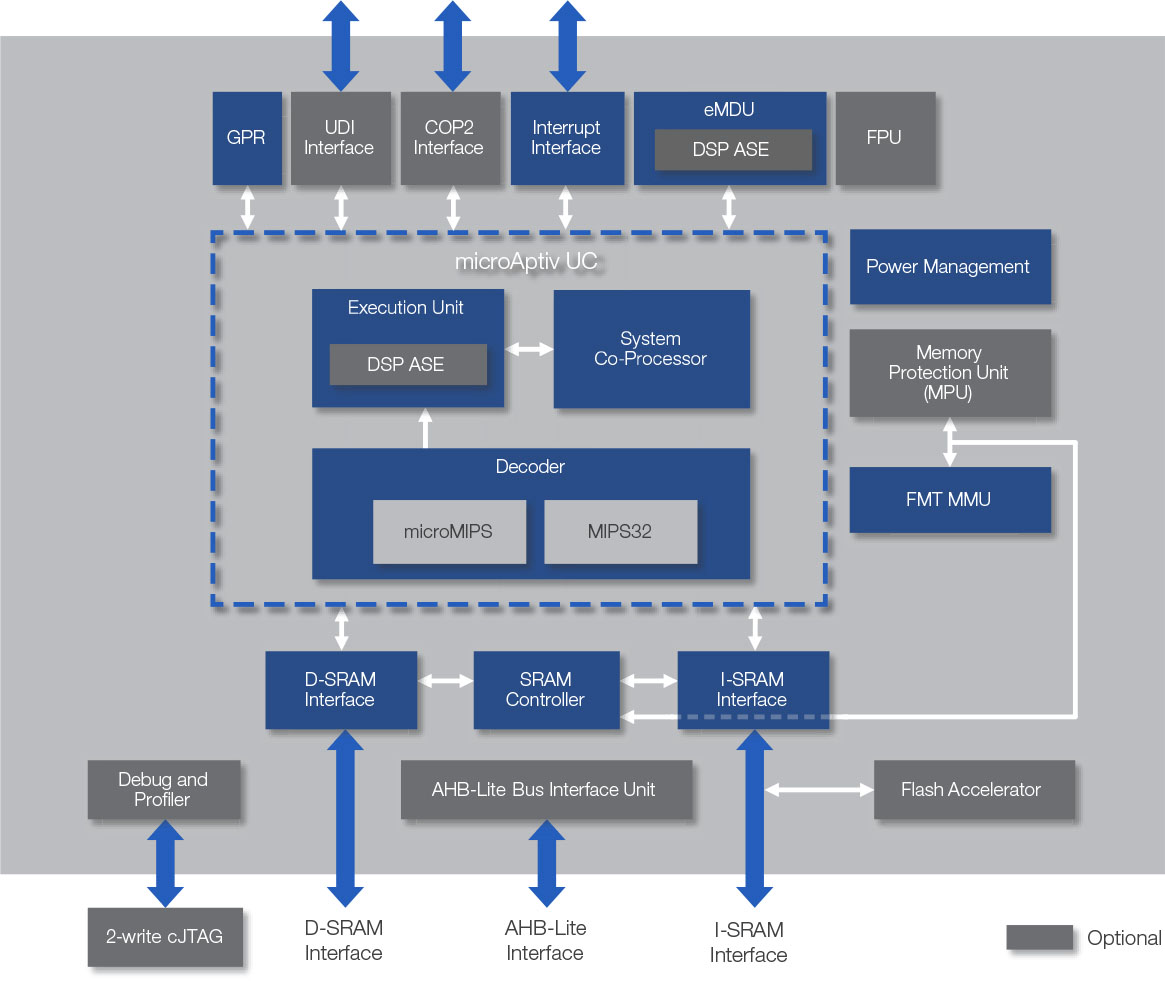

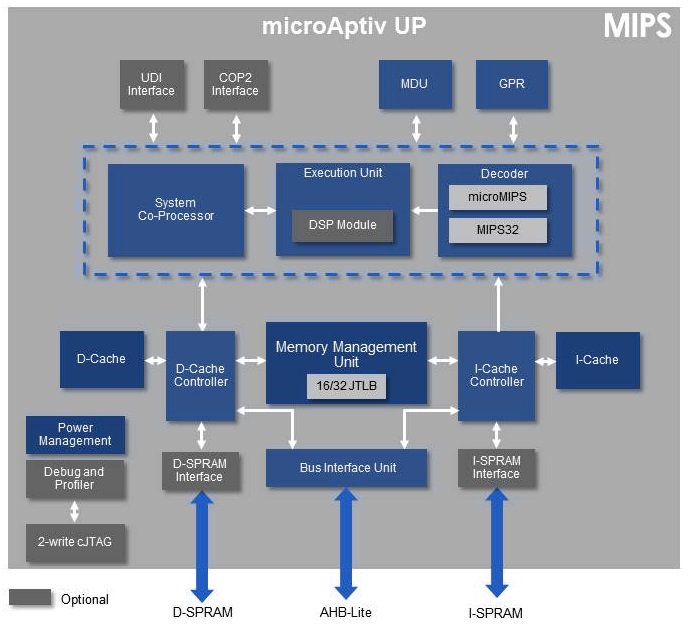

Considéré comme l’un des processeurs les plus compacts et les plus sobres de la famille Mips (et notamment utilisé par Microchip dans ses PIC32), le cœur Mips32 microAptiv cible le marché des microcontrôleurs temps réel et les applications embarquées d’entrée de gamme dans les secteurs de l’automobile, de l’Internet des objets et des équipements réseau résidentiels. Le code RTL Verilog des cœurs Mips32 microAptiv est d’ores et déjà téléchargeable (www.mipsopen.com/resources/download).

Considéré comme l’un des processeurs les plus compacts et les plus sobres de la famille Mips (et notamment utilisé par Microchip dans ses PIC32), le cœur Mips32 microAptiv cible le marché des microcontrôleurs temps réel et les applications embarquées d’entrée de gamme dans les secteurs de l’automobile, de l’Internet des objets et des équipements réseau résidentiels. Le code RTL Verilog des cœurs Mips32 microAptiv est d’ores et déjà téléchargeable (www.mipsopen.com/resources/download).

« Lorsque le cœur microAptiv a été lancé, il pouvait être cadencé à une vitesse d’horloge plus élevée que les autres cœurs de microcontrôleur et offrait une meilleure densité de code, indique Linley Gwennap, analyste de The Linley Group. Les concepteurs de puces-systèmes SoC peuvent désormais librement intégrer ce processeur fiable et puissant sans payer de redevances ou de frais de licence. » Le cœur Mips32 microAptiv est également doté de fonctions DSP et de mécanismes de compression de code qui permettent d’exécuter le logiciel avec un espace mémoire réduit.

Deux différentes versions du code RTL Verilog microAptiv sont disponibles. Le cœur microAptiv MCU (schéma ci-dessus), adapté au développement de puces-systèmes de classe microcontrôleur, est conçu avec des fonctionnalités spécifiques à l’application et affiche des performances temps réel. Le cœur microAptiv MPU (schéma ci-dessous), quant à lui, inclut un contrôleur de cache et une unité de gestion mémoire MMU et s’adresse aux conceptions embarquées qui exécutent des systèmes d’exploitation comme Linux.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée aux microcontrôleurs : Embedded-MCU https://www.linkedin.com/showcase/embedded-mcu/

-fr.jpg)