La firme britannique Imperas Software, spécialiste des plates-formes virtuelles et de la simulation logicielle, a mis à jour sa suite de tests de conformité pour le processeur open source RISC-V dans sa configuration de base référencée RV32I.... Mis au point conjointement avec le groupe de travail du comité technique de la fondation RISC-V chargé de la conformité, ces tests atteignent une couverture fonctionnelle à hauteur de presque 100%, selon ses promoteurs, pour le jeu d’instructions ISA RV32I. Cette suite a été téléchargée dans un référentiel GitHub de la RISC-V Foundation.

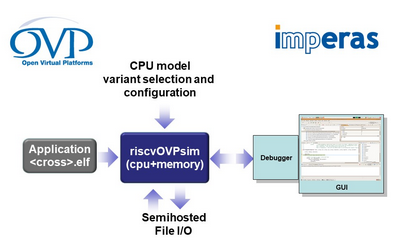

Parallèlement, Imperas a également mis à jour le simulateur gratuit riscvOVPsim (RISC-V Open Virtual Platform Simulator) en tant qu'implantation de référence du simulateur en open source (ISS, Instruction Set Simulator) du jeu d'instructions de l’architecture RISC-V, destinée aux utilisateurs (et aux développeurs) de la suite de tests de conformité. L’outil est lui aussi disponible sur GitHub.

« Actuellement, les groupes de travail RISC-V sont confrontés à de nombreux défis qui ne sont pas résolus par les principaux outils disponibles sur le marché, explique Allen Baum d'Esperanto Technologies qui préside le groupe de travail du comité technique de la Fondation RISC-V en charge de la conformité. L’équipe d’Imperas n’a pas seulement mis à jour les tests de conformité au jeu d'instructions RV32I au niveau d'un standard de référence, mais elle a également établi un cadre pour la couverture globale de test, alors que la fondation RISC-V continue de développer des tests pour les extensions optionnelles. »

« Actuellement, les groupes de travail RISC-V sont confrontés à de nombreux défis qui ne sont pas résolus par les principaux outils disponibles sur le marché, explique Allen Baum d'Esperanto Technologies qui préside le groupe de travail du comité technique de la Fondation RISC-V en charge de la conformité. L’équipe d’Imperas n’a pas seulement mis à jour les tests de conformité au jeu d'instructions RV32I au niveau d'un standard de référence, mais elle a également établi un cadre pour la couverture globale de test, alors que la fondation RISC-V continue de développer des tests pour les extensions optionnelles. »

« La vérification est importante pour toute implémentation de processeur, mais les tests de conformité RISC-V doivent en plus garantir un niveau d'interopérabilité sur l'ensemble de l'écosystème, précise Lee Moore, consultant principal et ingénieur conformité chez Imperas Software. En travaillant en étroite collaboration avec l'équipe Google Cloud sur le projet ISG (Instruction Set Generator), nous avons réalisé que les mêmes méthodes de couverture de test pourraient confirmer la qualité de la suite de la conformité RISC-V et aider ainsi à définir un test complet et exhaustif du jeu d’instructions de base RV32I. »

Imperas présentera un document technique sur ces travaux visant à développer et à étendre la suite de mesures de conformité et les dernières techniques de vérification au RISC-V Summit qui se déroulera du 10 au 12 décembre 2019 à San Jose (Californie).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV.

-dissolve-basic-fr.jpg)