Le britannique UltraSoC, qui s’est fait un nom sur le marché des IP d’instrumentation, de débogage et d’analyse de trace pour puces-systèmes, a pris la décision d’offrir via l’OpenHW Group une implémentation open source de son encodeur de trace RISC-V. ...Pour rappel, l’OpenHW Group, qui se veut un organisme à but non lucratif, s’est donné pour objectif d’accélérer l’adoption de processeurs open source via une plate-forme collaborative et la mise sur le marché de blocs d’IP open source pour cœurs de processeur (lire notre article ici).

La solution de trace RISC-V open source ainsi proposée sera 100% compatible avec le standard de trace de processeur actuellement en cours de développement au sein du groupe de travail ad hoc de la fondation RISC-V, précise UltraSoC. Disponible à la fin du premier trimestre 2020, elle comprendra les fonctionnalités de base qui devraient être incluses dans ce futur standard.

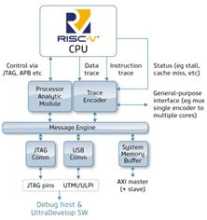

Globalement, les technologies d’analyse embarquées d’UltraSoC permettent notamment de surveiller et d'analyser le comportement de presque toutes les structures sur puce, y compris les cœurs de processeurs, les interconnexions et les réseaux intégrés dans la puce et même la logique personnalisée. La structure de supervision laisse aussi à l'architecte système libre choix sur les IP tierces parties à intégrer, les parties du design qui doivent être personnalisées et la manière d’interconnecter la puce-système. Cette approche « ouverte » de l'offre commerciale d’UltraSoC se reflète désormais dans la disponibilité d'un outil open source de qualité professionnelle pour le suivi et le débogage de processeurs, précise la société britannique. Cette dernière compte aussi soutenir la version open source de son offre avec une licence d’évaluation de sa suite d'outils UltraDevelop, qui fournit un environnement sur Eclipse où les données comportementales de n'importe quelle puce peuvent être capturées et visualisées.

Globalement, les technologies d’analyse embarquées d’UltraSoC permettent notamment de surveiller et d'analyser le comportement de presque toutes les structures sur puce, y compris les cœurs de processeurs, les interconnexions et les réseaux intégrés dans la puce et même la logique personnalisée. La structure de supervision laisse aussi à l'architecte système libre choix sur les IP tierces parties à intégrer, les parties du design qui doivent être personnalisées et la manière d’interconnecter la puce-système. Cette approche « ouverte » de l'offre commerciale d’UltraSoC se reflète désormais dans la disponibilité d'un outil open source de qualité professionnelle pour le suivi et le débogage de processeurs, précise la société britannique. Cette dernière compte aussi soutenir la version open source de son offre avec une licence d’évaluation de sa suite d'outils UltraDevelop, qui fournit un environnement sur Eclipse où les données comportementales de n'importe quelle puce peuvent être capturées et visualisées.

« Nous croyons dans les standards industriels et à l'importance de l'open source, indique Rupert Baines, le CEO d'UltraSoC. En faisant don à l’OpenHW Group de notre encodeur de trace, nous pouvons contribuer à l'adoption de l’architecture RISC-V par l'industrie, renforcer l'écosystème et soutenir la compatibilité et la cohérence de l’offre. L'open source est un modèle familier dans le monde du logiciel, mais dans le matériel, nous commençons tout juste à débloquer les opportunités liées à cette approche. La disponibilité du jeu d’instructions RISC-V a donné une impulsion initiale, et des organismes tels que l’OpenHW Group vont maintenant aller plus loin. Parallèlement un cadre juridique a été mis en place pour que les sociétés proposant des blocs d’IP matériels tel UltraSoC puissent concéder leurs technologies sous licence en toute confiance. » Créé début 2019, l’OpenHW Group propose sous l’appellation CORE-V une famille de cœurs de processeur RISC-V de qualité professionnelle sur une base open source, avec les blocs d’IP, les outils et les logiciels associés et ce pour des implémentations sur silicium ou sur FPGA (lire nos articles ici et ici).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV