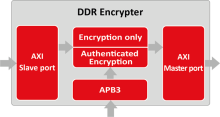

Spécialiste des blocs d’IP de sécurité pour FPGA, circuits Asic et puces-systèmes SoC, Silex Insight a étoffé son offre avec un bloc de chiffrement DDR à haut débit (100 Gbit/s), destiné typiquement à se placer entre un processeur et un contrôleur de mémoire externe (DDRx). Selon la société belge, le module DDR Encrypter IP Core permet le chiffrement et l'authentification à la volée des données de la mémoire externe. Configurable, il peut être optimisé pour se plier à des exigences en matière d’empreinte silicium, de débit et de latence.

Silex Insight rappelle que de nombreux Asic/FPGA s’avèrent désormais être des puces-systèmes qui contiennent des blocs de traitement intégrés gravés dans le silicium. Lorsque la confidentialité des données est essentielle, il est nécessaire de protéger la confidentialité des accès mémoire effectués par le processeur (extractions d'instructions, transactions génériques, etc.). Dans ce cadre, le bloc d’IP de Silex Insight, qui peut être fourni en option avec une fonction d’authentification, améliore la résistance aux falsifications en évitant toute modification, usurpation ou analyse de données externes.

« Nous avons reçu de nombreuses demandes du marché pour proposer un bloc de chiffrement DDR à très haut débit qui puisse être intégré non seulement dans les Asic, mais aussi dans les FPGA comme les modèles UltraScale+ et Versal de Xilinx, indique Sébastien Rabou, le directeur technique de Silex Insight. L'architecture de notre DDR Encrypter garantit un niveau élevé de flexibilité et permet son intégration dans des architectures de microcontrôleurs et de processeurs multicœurs. »

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à la sécurité dans les systèmes embarqués : Embedded-SEC