Fondé par les créateurs de l’architecture de processeur open source RISC-V à l’université de Californie à Berkeley et spécialiste des cœurs d’IP RISC-V, l’américain SiFive annonce la disponibilité de sa famille E2, constituée de cœurs de microcontrôleur configurables à la fois basse consommation et de faible empreinte silicium, ...conçus pour une utilisation au sein de systèmes embarqués.

Le modèle E21 fournit des performances classiques adaptées aux besoins du marché des microcontrôleurs, de la fusion de capteurs, des cœurs d’appoint (pour le traitement des tâches d’entrées/sorties par exemple) et des objets connectés. Le modèle E20, quant à lui, est présenté comme le cœur standard de SiFive le plus éco-efficace et peut être utilisé au sein de microcontrôleurs généralistes, de processeurs de traitement du signal mixtes et de machines à états finis.

Le modèle E21 fournit des performances classiques adaptées aux besoins du marché des microcontrôleurs, de la fusion de capteurs, des cœurs d’appoint (pour le traitement des tâches d’entrées/sorties par exemple) et des objets connectés. Le modèle E20, quant à lui, est présenté comme le cœur standard de SiFive le plus éco-efficace et peut être utilisé au sein de microcontrôleurs généralistes, de processeurs de traitement du signal mixtes et de machines à états finis.

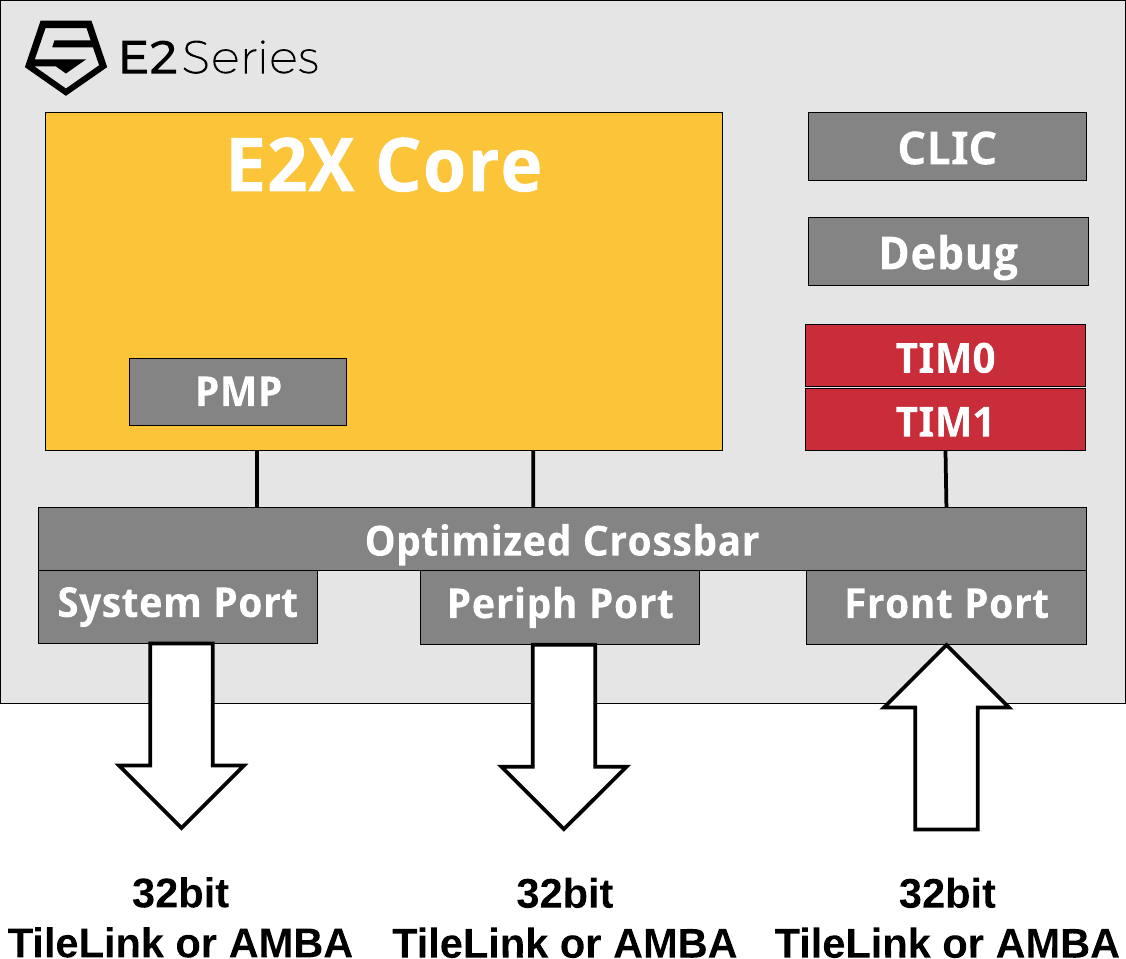

100% compatibles avec les piles logicielles, les outils, les compilateurs et l’écosystème RISC-V qui s’étoffent inexorablement depuis le lancement par SiFive de ses premiers cœurs RISC-V en 2016, les deux cœurs sont synthétisables et implémentés en tant qu’IP logicielles dûment vérifiées. Ils disposent de fonctionnalités avancées telles qu’une organisation mémoire entièrement configurable, de multiples ports également configurables, une mémoire d’instructions étroitement intégrée (TIM), des accès rapides en entrées/sorties et un nouveau contrôleur d’interruptions (CLIC) garant de temps de réponse aux interruptions extrêmement rapides avec mécanismes de priorisation au niveau matériel et de préemption.

SiFive offre par ailleurs la possibilité aux concepteurs de configurer les cœurs selon leurs besoins applicatifs en termes de performances, de fonctionnalités de la microarchitecture, d'empreinte silicium, de sous-systèmes mémoire, etc.

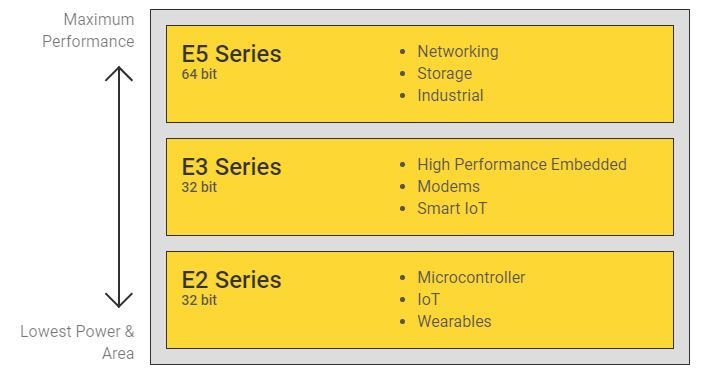

Parallèlement à l’annonce des cœurs E2, la société californienne a étoffé ses gammes de cœurs E3 et E5 afin qu’elles puissent prendre en charge des configurations multicœurs cohérentes dans des applications embarquées hautes performances (stockage, industriel, modems, infrastructures réseau…). Les modèles E3 (32 bits) et E5 (64 bits) bénéficient en outre d’une unité de multiplication évoluée que leur permet d’atteindre une performance de 3 CoreMarks/MHz même avec des compilateurs GCC open source.