Selon la firme japonaise eSOL, qui édite des solutions logicielles embarquées temps réel, la technologie SHIM (Software-Hardware Interface for Multi-Many Core) a été officialisée en tant que norme IEEE sous la référence IEEE 2804-2019.... Cette spécification est issue des travaux du groupe de travail IEEE C/DA/SHIM WG créé en février de l'année dernière mais plonge ses racines dans la mise en place en 2013 par la Multicore Association d’un groupe de travail dont l’objectif était justement de fournir la description d’une interface commune aux architectures multicoeurs pour les éditeurs d’OS et d’outils logiciels. La Multicore Association a été créée en 2005 pour promouvoir l’usage des architectures à multiples cœurs dans l’embarqué.

Le rôle du groupe de l’IEEE était donc de travailler à la normalisation des descriptions d’architecture matérielle multicoeur du point de vue de la conception de logiciels. Masaki Gondo, directeur technique et directeur général d'eSOL, a ici joué un rôle central dans la formulation de la norme, servant en tant que président du groupe de travail et apportant des contributions qui ont abouti à sa publication.

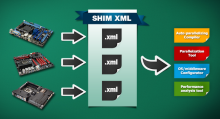

.png) Le document décrit l'interface logicielle-matérielle pour plusieurs noyaux et fournit des schémas XML qui synthétisent les propriétés matérielles clés essentielles à l'activation d’outils logiciels. L’idée sous-jacente étant de réduire les coûts de prise en charge d’une architecture à plusieurs cœurs par la plupart des outils logiciels du commerce.

Le document décrit l'interface logicielle-matérielle pour plusieurs noyaux et fournit des schémas XML qui synthétisent les propriétés matérielles clés essentielles à l'activation d’outils logiciels. L’idée sous-jacente étant de réduire les coûts de prise en charge d’une architecture à plusieurs cœurs par la plupart des outils logiciels du commerce.

eSOL, largement à l’origine de cette norme IEEE, a développé en 2012 un système d’exploitation temps réel (RTOS) destiné aux processeurs multicœurs. Commercialisé sous le nom de eMCOS, ce RTOS met en œuvre une architecture de micronoyau distribuée et intègre un algorithme d'ordonnancement propriétaire. De plus, eSOL avait auparavant développé l'eT-Kernel Multi-Core Edition (MCE), un RTOS pour processeurs multicœurs qui permet notamment aux sous-systèmes SMP et AMP de coexister au sein d’un même système.

D’ores et déjà les outils comme le paralléliseur fondé sur le modèle eMBP développé par eSOL, en partenariat avec l'université de Nagoya au Japon, et l’outil SLX de Silexica sont en conformité avec la norme IEEE 2804 leur permettant de fournir une prise en charge rapide des nouvelles puces multinoyaux issues de différents fournisseurs.

-dissolve-basic-fr.jpg)