[APPLICATION GOWIN] Le marché est désormais prêt à recevoir une nouvelle génération de FPGA d’entrée de gamme économiques dans des appareils grand public mais capables d’exploiter des émetteurs-récepteurs haut débit comme les Serdes. Et ce en vue de répondre aux besoins actuels et futurs des caméras et écrans en ultra haute définition qui potentiellement intégreront de plus en plus de périphériques haut débit afin de prendre en charge de nouvelles fonctionnalités et cas d’usage tirés par l’intelligence artificielle, ainsi que les applications de réalité augmentée et virtuelle. Or pour ses applications complexes, le marché du FPGA ne proposait pas jusqu’à aujourd’hui des circuits répondant aux exigences de débit/coût/taille du marché grand public. Mais la situation évolue, comme l’explique ici Gowin, en s’appuyant notamment sur des nœuds de fabrication en 22 nm.

Auteur : Jason Zhu,

Auteur : Jason Zhu,

Directeur général Gowin Semiconductor

Lorsqu’un concepteur d’équipement télécoms tels qu’un serveur ou un commutateur spécifie un FPGA pour une fonction d'interface de données haut débit, la performance est le critère le plus important dans le choix. Et si la règle de base pour spécifier un composant électronique est que le concepteur ne s’appuie que sur un ou deux attributs (haut débit, basse consommation, format réduit et prix abordable) mais pas trois ou quatre, le fabricant de l’équipement télécoms privilégiera toujours le haut débit. Ce qui a fortement incité les fabricants de FPGA haut de gamme et haute densité à développer des produits avec des capacités SerDes élevées prenant en charge les protocoles de communication haut débit – PCIe, Ethernet, Infiniband, etc. – sur lesquels les réseaux de fibre optique des prestataires de service de communication sont fondés.

Ces FPGA peuvent être volumineux, coûteux et énergivores mais cela importe peu aux fabricants d’équipements desservant le marché des télécoms, tant qu’ils sont rapides. La question est tout autre sur le marché des appareils grand public portables, sur lesquels le coût, la consommation d’énergie et l’encombrement d’un FPGA ne peuvent être négligés. Ains, le rôle des FPGA dans les appareils grand public se limitait jusqu’à aujourd’hui à des fonctions que les FPGA de base à format réduit, basse consommation, basse densité et prix abordable, pouvaient remplir. En particulier l’intégration de la logique de raccordement, la présence d’un compteur simple, d’une machine d’état, d’une logique de contrôle, de liens pour les entrées/sorties et diverses interfaces. Avec en sus la possibilité d’extension pour les entrées/sorties, la possibilité d’agréger plusieurs entrées de capteurs et la présence d’un dispositif de surrveillance de tension.

Pour des applications plus complexes, le marché FPGA ne proposait pas auparavant de produits répondant aux exigences de débit/coût/taille du marché grand public. De fait, il n’existait pas de demande pour des capacités d’interface haut débit des FPGA tant que les appareils grand public comme des appareils photo d’entrée de gamme ou de petits écrans géraient des quantités de données relativement limitées à travers la prise en charge d’entrées/sorties peu exigeantes. Mais la situation évolue

Besoin de débits élevés sur des cirtuits abordables

Cependant, aujourd’hui l’univers du consommateur n'est plus le même : la technologie et la demande accélèrent le besoin en débit de données de façon très significative. On découvre alors qu’il n’existe pratiquement plus de limites à l’appétit du public pour de la vidéo nette et ultra haute définition et des images haute résolution dopées à l’intelligence artificielle, même dans des produits portables offrant peu d’espace et de puissance tels que les casques de réalité augmentée/virtuelle et les lunettes connectées.

À titre d’exemple, un casque de réalité virtuelle devra généralement accepter un type de contenu UHD habituellement vu sur un grand écran de télévision, voire deux écrans synchronisés. Non seulement il doit proposer une résolution 4K, voire 8K, mais il doit également afficher un rendu avec une fréquence d’images plus élevée – généralement 120 images/s – qu’une télévision standard, afin d’éviter le risque de flou de mouvement.

Pour créer des expériences immersives, un casque de réalité virtuelle nécessite des capacités d’affichage ultra haute définition et la bande passante interne correspondante

Pour créer des expériences immersives, un casque de réalité virtuelle nécessite des capacités d’affichage ultra haute définition et la bande passante interne correspondante

Cette exigence de bande passante vidéo supérieure pousse les fabricants d’appareils à migrer vers des interfaces de type MIPI D-PHY pour la vidéo et vers des alternatives à plus haut débit telles que MIPI C-PHY ou DisplayPort. Ce qui oblige à augmenter les capacités SerDes haut débit identiques à celles que le concepteur d’équipement télécoms recherche dans un FPGA. Or, nous savons que les FPGA mis au point pour le marché des télécoms ne conviennent pas aux appareils grand public.

C’est pourquoi on commence à entrevoir l’émergence d’une nouvelle catégorie de FPGA pour le segment basse densité et d’entrée de gamme du marché qui se limitait précédemment à des fonctions logiques de base. Ces FPGA nouvelle génération sont optimisés pour des fonctions SerDes haut débit.et ils proposent non seulement des capacités SerDes haut débit brutes mais prennent également spécifiquement en charge les protocoles que les nouveaux appareils grand public utilisent - MIPI C-PHY et PCIe - sous forme de blocs d’IP codés par le logiciel ou même directement implantés au niveau matériel dans le silicium.

Ces capacités SerDes reposent notamment sur une mémoire haut débit plus généreuse que d’habitude dans les FPGA bas de gamme.

Exemples de cas d’usage de traitement et liaison vidéo dans les derniers appareils grand public

Optimisée pour les fonctions d’interface et de liaison de données, cette nouvelle génération de FPGA aura une portée limitée pour la mise en œuvre d’autres fonctions logiques au-delà de quelques éléments logiques à visée générale disponibles sur l’application, et ce afin de minimiser la taille et la coût du circuit.

Du point de vue de Gowin Semiconductor, ces FPGA exigent un changement de stratégie de la part des fabricants de circuits programmables basse densité. À ce jour, ils sont parvenus à répondre aux exigences de bas coût en prolongeant la durée de vie des anciens nœuds de processus utilisés pour fabriquer leurs produits, à l’aide d’un processus 40 nm ou plus ancien, pour lequel l’investissement en équipement et en masques est relativement faible.

A ce niveau, Gowin occupe une position relativement solide sur le marché des appareils grand public avec sa gamme de FPGA basse densité LittleBee qui sont fabriqués sur un processus ancien. Les FPGA LittleBee exécutent une fonction d’agrégation de données dans de nombreux appareils portables et mobiles. Sans cette fonction, les données issues des capteurs seraient transférées au microcontrôleur principal ou à une puce-système (SoC, System On Chip) et les données de commande ou de configuration seraient transférées du SoC aux capteurs à travers des interfaces bas débit tels qu’I2C, UART ou SPI fonctionnant comme des canaux de communication en bande latérale.

Ce qui se traduit par lune prolifération de câbles entre le SoC et les sous-systèmes de capteurs, souvent montés sur une carte distincte de la carte de contrôleur principale. En mettant en œuvre l’agrégation de données dans un FPGA, les données de plusieurs capteurs peuvent être combinées dans un seul flux de données haut débit, réduisant le nombre de connexions réseau physiques entre l’hôte et les différents sous-systèmes.

Concernant les serveurs, le projet en open source OCP DC-SCM est un exemple de mise en œuvre de ce principe d’agrégation de données.

Vers un procédé de fabrication du FPGA d'entrées de gamme en 22 nm

On le voit, bien que les processus de fabrication anciens puissent être adaptés pour l’agrégation des interfaces I2C, UART ou SPI bas débit, ils ne répondent cependant pas aux exigences des circuits SerDes avancés. Ainsi, à titre d’exemple, la spécification MIPI C-PHY prend en charge un débit de données jusqu’à 13,7 Gops (*) procurant jusqu’à trois fois la bande passante de la norme MIPI D-PHY précédente.

C’est pourquoi Gowin a pris la décision radicale de passer à un nœud avancé – un process de fabrication en 22 nm ultra basse consommation chez TSMC – pour sa gamme de FPGA basse densité Arora V. Ce process en 22 nm a permis à Gowin d’intégrer un émetteur-récepteur haut débit sur puce au sein des FPGA Arora V. Il a également permis d’inclure une mémoire plus conséquente.

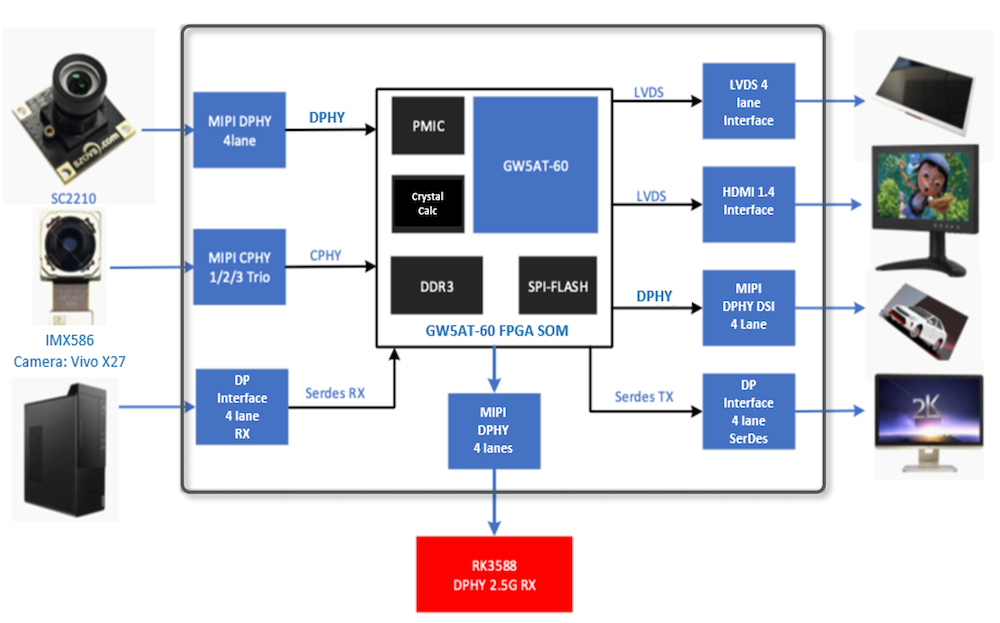

En passant du nœud 55 nm utilisé pour les FPGA LittleBee au 22 nm, la taille de la cellule mémoire rétrécit de 80 %. La conséquence pratique de l’adoption de la conception 22 nm est directement visible dans les spécifications du produit Arora V GW5AT-60. Ce circuit intègre quatre émetteurs-récepteurs prenant en charge une plage de débit de données de 270 Mops jusqu’à 12,5 Gops et une interface MIPI D-PHY matérielle propose quatre canaux de données, tandis qu’une MIPI C-PHY matérielle contient trois canaux de données.

Les interfaces logicielles incluent le PCIe 2.0 (avec 1, 2 et 4 canaux), et le LVDS jusqu’à 1,25 Gops, ainsi qu’une interface mémoire DDR3 opérant jusqu’à 1 333 Mops. La mémoire inclut 118 blocs de SRAM de 2 124 ko de type bloc et 468 ko de SRAM parallèle. Le FPGA inclut également des éléments logiques jusqu'à 460 K de tables LUT. La tension centrale de l’appareil est de 0,9 V/1,0 V/1,2 V.

Ces caractéristiques illustrent la façon dont, en utilisant un nœud de fabrication avancé, il devient possible de créer un FPGA basse densité et basse consommation qui fournit une interface de données haut débit. En outre, du fait de sa taille réduite, ce FPGA peut être proposé à un prix unitaire abordable dans des appareils grand public portables.

De fait, le coût est suffisamment intéressant pour que les équipementiers puissent utiliser le FPGA dans la production en série, sans avoir à envisager de le remplacer par un ASIC personnalisé, une étape chronophage et risquée que les équipementiers préfèrent souvent éviter. L’engagement pour une filière silicium avancée dans une gamme de produits qui inclut des FPGA bas de gamme pousse maintenant le marché dans une autre direction qui associe les capacités d’émetteur-récepteur haut débit des FPGA de télécoms traditionnels aux prix économique et à la faible consommation d’énergie des FPGA d’entrée de gamme traditionnels.

(*) Débit de données MIPI C-PHY maximum, extrait de : https://www.mipi.org/specifications/c-phy