Issu du projet de recherche industriel Flodam, l’outil Diafim du français Temento Systems vise à tester la vulnérabilité des circuits Asic ou des blocs d’IP vis-à-vis des rayonnements ionisants, potentiellement nuisibles et de plus en plus présents dans l’atmosphère. Et ce au niveau de la conception, c’est-à-dire avant de réaliser des essais sur un prototype. La technologie cible les concepteurs de systèmes électroniques embarqués critiques en matière de sûreté de fonctionnement qui doivent valider que le cœur de leur système (Asic, FPGA ou processeur) est suffisamment tolérant aux fautes causées par les impacts des particules ionisantes.

Pour rappel, ces rayonnements ionisants (protons, neutrons, particules alpha, etc.) peuvent provoquer des changements d’états sur les éléments logiques d’un circuit et par conséquent induire des défauts de type SEU (Single Event Upset) ou SET (Single Event Transient). Ces SEU/SET peuvent entraîner divers effets, jusqu’à un dysfonctionnement du circuit.

A l’origine de la technologie se trouve donc le projet Flodam, associant Temento et les organismes de recherche Inria et Onera, et centré sur la problématique du durcissement des architectures de processeurs multicœurs embarqués. Il s’agissait de mettre à disposition des fabricants de semi-conducteurs et des concepteurs de systèmes embarqués critiques, présents dans l’avionique, l’automobile, le ferroviaire, la Défense, le nucléaire ou le médical, une méthodologie et des outils qui permettent d’élever leur niveau de fiabilité vis-à-vis des rayonnements d’origine naturelle (*), leur niveau d’intégration les rendant plus fragiles face à ce phénomène.

Pour tester ces circuits, les méthodes traditionnelles consistent soit à les tester physiquement sous rayonnement ionisant, une technique longue et coûteuse, soit à réaliser des injections de fautes par simulation au niveau des portes logiques du circuit, une approche qui nécessite de fortes puissances de calcul et des temps de traitement très longs.

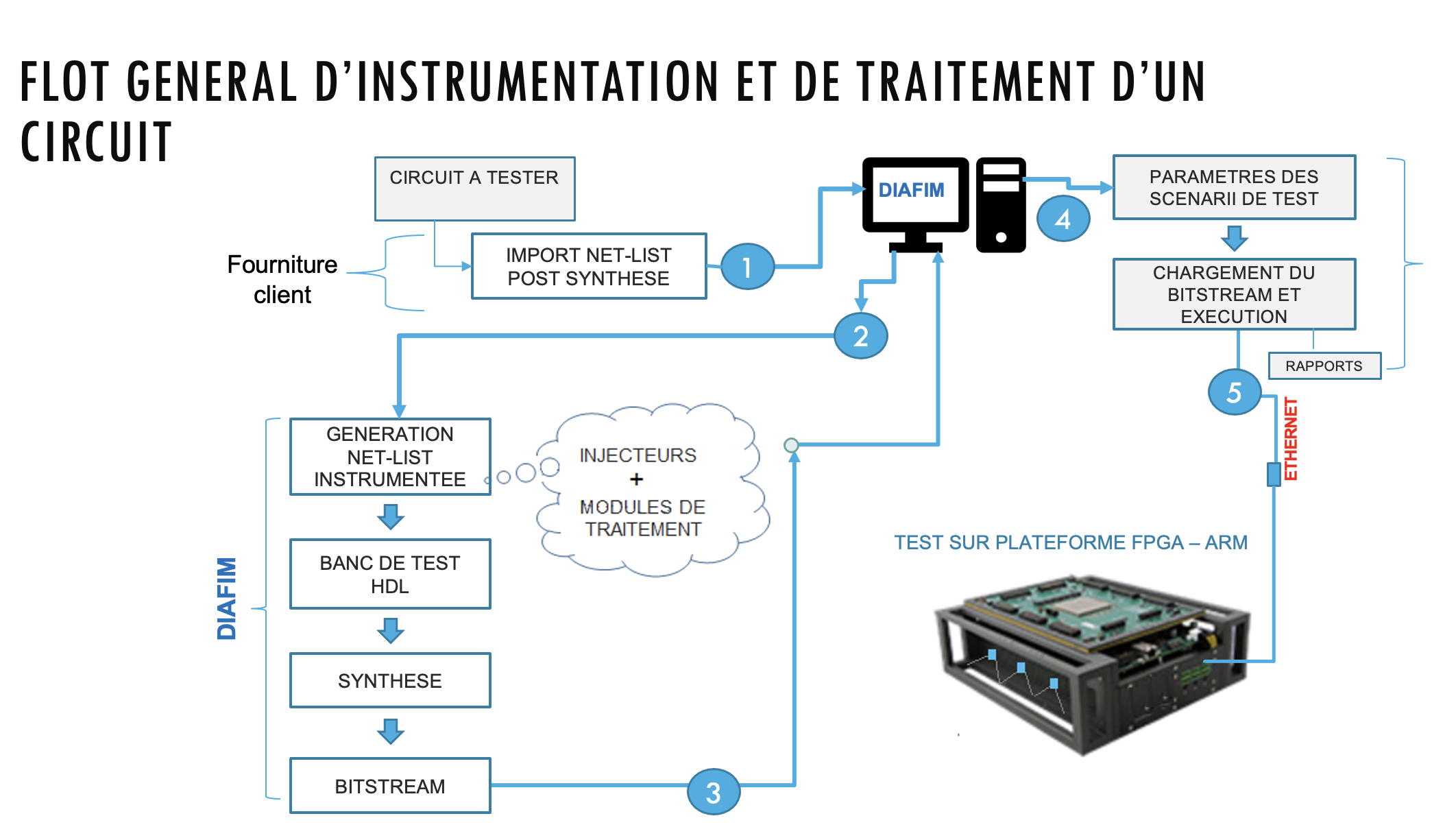

L’approche de Diafim est de réaliser des tests par émulation sur une plateforme FPGA dans laquelle la conception du circuit à tester est implantée. Ici l’injection de fautes permet d’exécuter un grand nombre de campagnes de test avec un ciblage très précis de la zone d’injection, et une rapidité d’exécution des tests. De fait, selon Temento, la solution accélère les vérifications et autorise l’injection de fautes logiques à la vitesse de fonctionnement du circuit sur le FPGA cible, de manière beaucoup plus rapide qu’une simulation HDL. Avec en sus la possibilité de faire tourner un grand nombre de scenarii de test, et donc de comparer rapidement différentes options de durcissement. Cette vérification du durcissement au niveau de la conception diminue en outre le nombre d’essais physiques sous radiations à réaliser.

Concrètement, avec DiaFim, le circuit ou le bloc d’IP à tester est instrumenté avec des injecteurs de fautes qui sont placés devant chaque bascule flip-flop d’un circuit. Le design du circuit et les modules de traitement associés sont ensuite chargés sur une plateforme FPGA, tandis que des scenarii de test (type d’injection, durée, moments d’injection etc.) sont préparés en amont et appliqués sur le circuit. Les résultats du déroulement d’un scénario de test sont alors comparés avec un ou plusieurs scénarios d’injections de fautes par rapport à un même scénario sans injection, et un rapport est généré automatiquement avec des statistiques relatives aux erreurs détectées et à la couverture de test.

L’ensemble permet de détecter les fautes de type SEU, MBU (Multi Bit Upset) et SET et de repérer des défauts de comportements, comme le crash (arrêt complet du système), le "hang" (boucle infinie) ou l’AOM (Application Output Mismatch) où une sortie s'avère différente de la référence.

(*) Ces rayonnements sont définis dans la norme CEI 62396