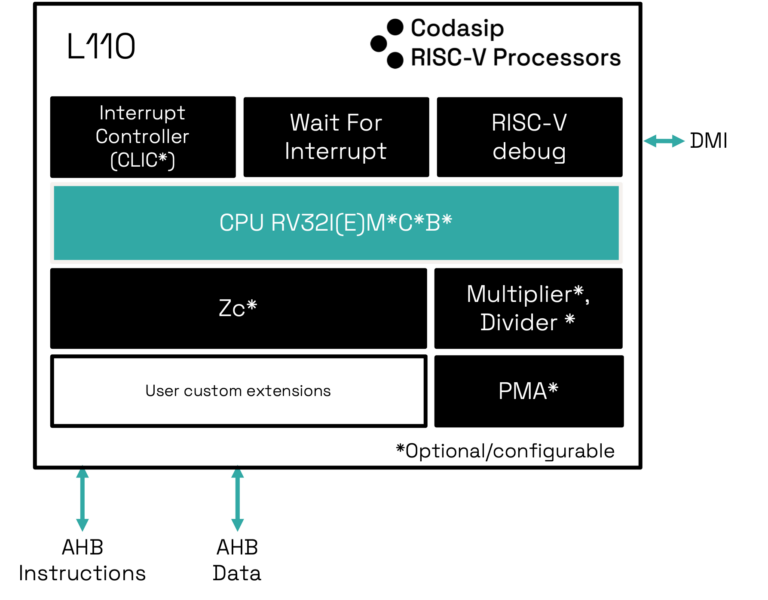

Spécialiste des cœurs de processeur embarqués RISC-V personnalisables destinés aux concepteurs de puces-systèmes, Codasip dévoile sous la référence L110 un nouveau cœur basse consommation qui, selon la société, se distingue par une amélioration jusqu’à 50% du rapport performances/watt par rapport aux offres similaires du marché, ainsi que par une taille du code réduite de 20%. En outre, les utilisateurs peuvent y ajouter leurs ajustements particuliers pour optimiser les critères de consommation, de performances et de surface silicium PPA (Power, Performance and Area) pour leurs applications spécifiques.

Ce niveau de personnalisation est soutenu par une nouvelle option de l’outil Codasip Studio Fusion, dénommée Bounded Customization, qui, selon la société, permet une mise sur le marché rapide de cœurs RISC-V de haute qualité et entièrement vérifiés. Le cœur peut être ainsi étendu avec de nouvelles instructions sans risque, car la fonctionnalité du coeur de base est garantie, assure Codasip, sachant qu’un framework de vérification associé simplifie considérablement la vérification des instructions personnalisées.

Conçu par l'équipe de Codasip à l'aide de l’environnement Codasip Studio Fusion, le cœur L110 est idéal pour les applications compactes à faible consommation, telles que le remplacement de machines d'état, les contrôleurs de capteurs et la périphérie des réseaux IoT.

Conçu par l'équipe de Codasip à l'aide de l’environnement Codasip Studio Fusion, le cœur L110 est idéal pour les applications compactes à faible consommation, telles que le remplacement de machines d'état, les contrôleurs de capteurs et la périphérie des réseaux IoT.

Codasip rappelle que l’environnement Codasip Studio Fusion permet aux utilisateurs de configurer le cœur à partir d'options définies, de créer des instructions personnalisées dans des limites définies ou de concevoir librement. Les outils génèrent automatiquement un SDK (Software Development Toolkit) comprenant un compilateur, des modèles de simulation, un débogueur et un analyseur de performances, ainsi qu'un HDK (Hardware Development Kit) comprenant un outil de conception RTL (Register Transfer Level), un framework de vérification, etc.

La dernière version en date introduit davantage d'automatisation pour rendre la conception des processeurs encore plus simple et plus rapide, assure Codasip. Ainsi de nouvelles constructions de conception permettent de fusionner la description architecturale et microarchitecturale du processeur. L'ensemble d'outils peut également convertir automatiquement les descriptions déclaratives des aspects courants du processeur en logique de bas niveau.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV