A l’occasion du salon Electronica 2024, qui se tient du 12 au 15 novembre à Munich (Allemagne), Renesas a levé le voile sur une nouvelle génération de puces-systèmes automobiles dites de « fusion », capables de répondre aux besoins de différents domaines d’un véhicule, des systèmes évolués d'assistance à la conduite (ADAS) à l'infodivertissement embarqué (IVI) en passant par les applications de passerelle, et ce avec un seul et même circuit intégré.

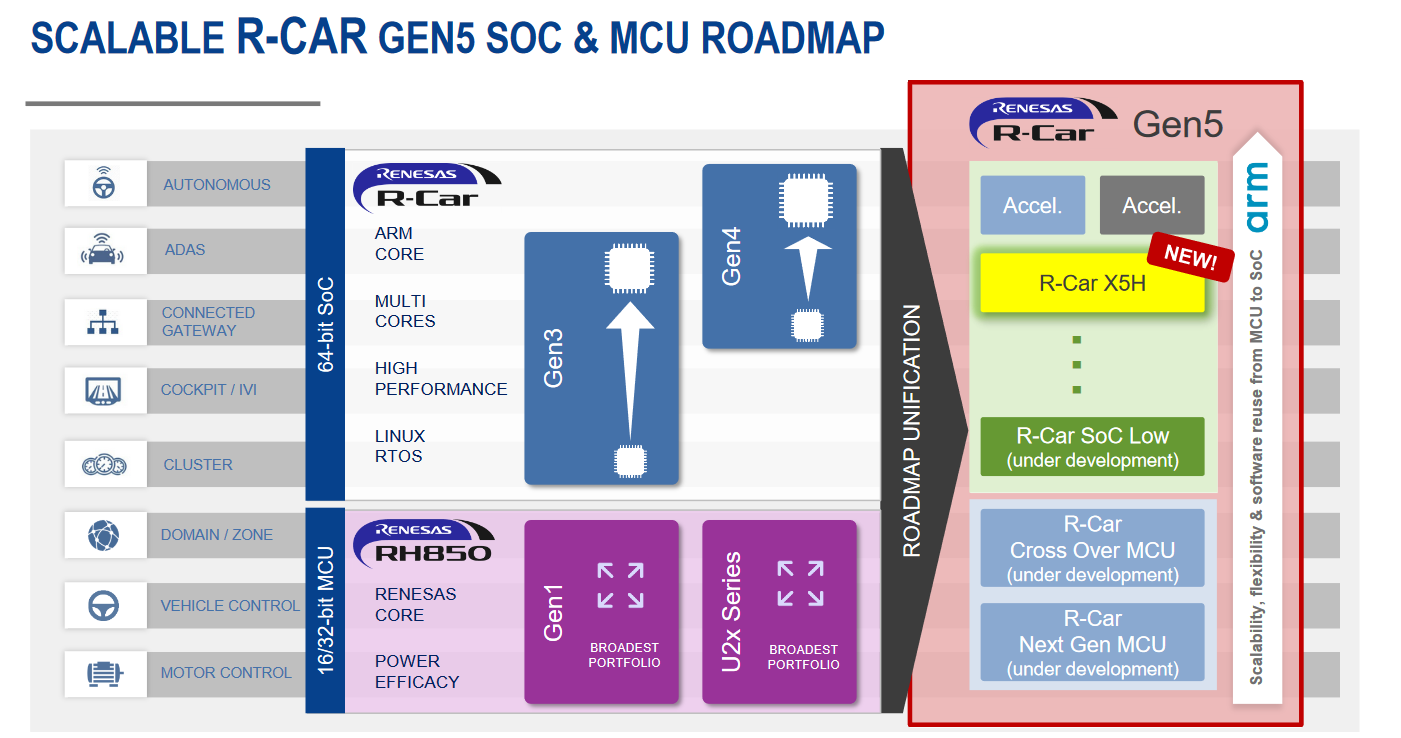

Gravé en technologie 3 nm, le SoC R-Car X5H, qui est le premier composant de la série R-Car X5 (de cinquième génération), devrait être échantillonné auprès de clients automobiles triés sur le volet au cours du premier semestre 2025 (pour une mise en production dans la seconde moitié de l’année 2027).

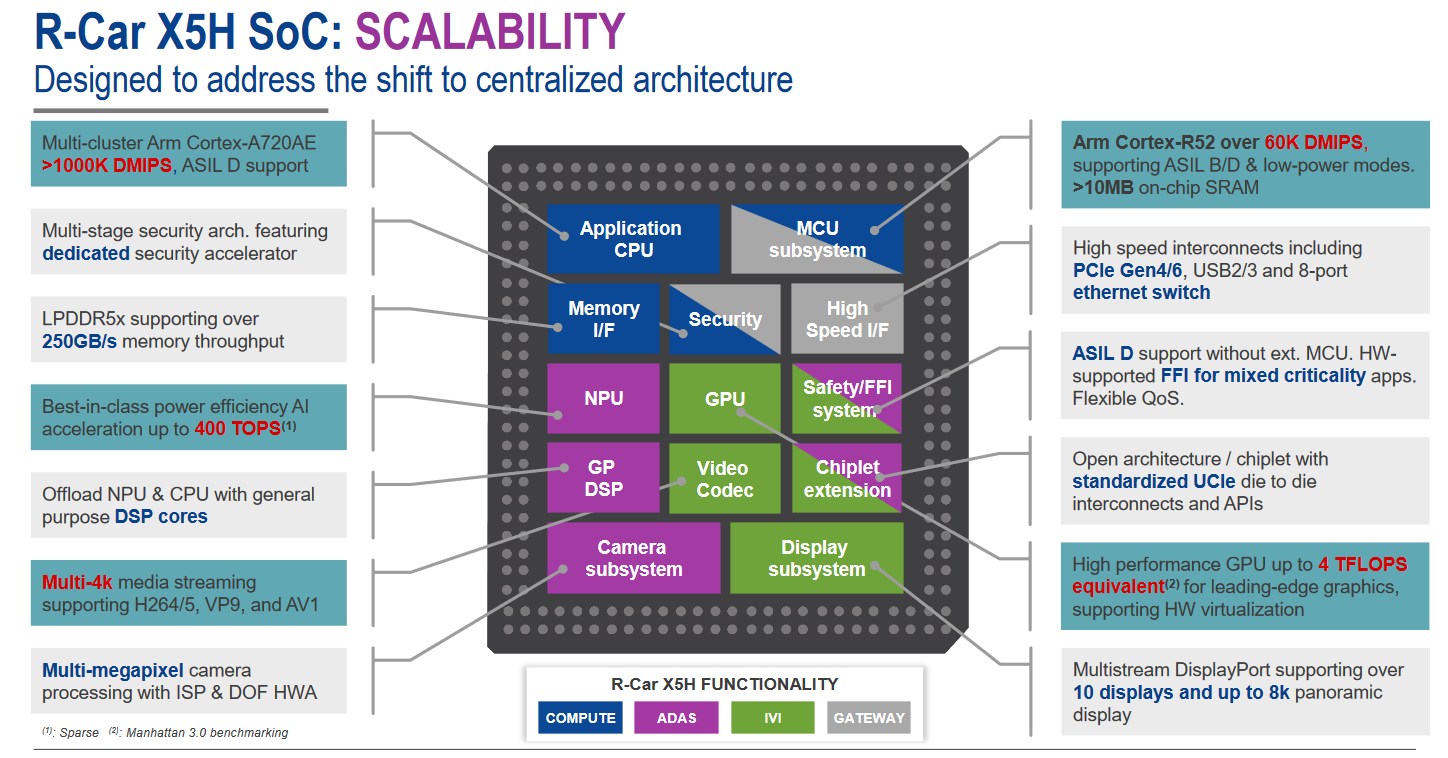

Selon Renesas, le R-Car X5H offre le plus haut niveau d'intégration et de performance de l'industrie et doit permettre aux constructeurs et équipementiers de premier rang de passer à des unités de contrôle électronique (ECU) centralisées. Dans la pratique, la puce intègre un total de 32 cœurs Arm Cortex-A720AE pour le traitement applicatif (pour une performance de plus d’un million de DMips) et six cœurs Arm Cortex-R52 en mode double lockstep (pour une performance de plus de 60 000 DMips avec prise en charge des contraintes de sûreté de fonctionnement de niveau Asil-D sans recourir à des microcontrôleurs externes).

Grâce au procédé de gravure TSMC 3 nm, les puces R-Car X5H seraient ainsi en mesure d’atteindre des performances CPU très haut de gamme tout en affichant une réduction de 30 à 35 % de la consommation d'énergie par rapport aux produits conçus en technologie 5 nm.

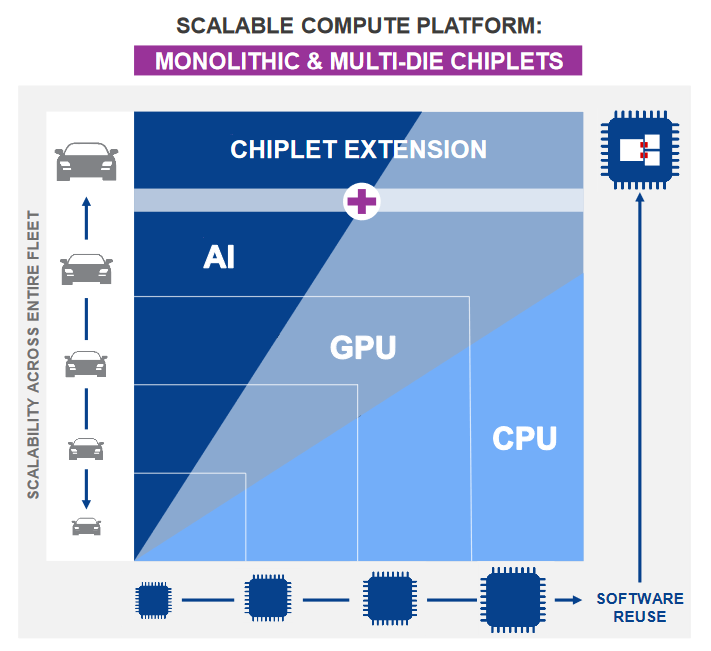

Au-delà, affirme Renesas, les nouveaux SoC, dotés de moteurs de traitement NPU et GPU natifs, sont en mesure d’offrir des capacités d’accélération IA jusqu'à 400 Tops (téraopérations par seconde) avec un rapport Tops/W sans équivalent dans l'industrie, ainsi que des performances de traitement graphique jusqu'à 4 TFlops. Sachant que les R-Car X5H offrent la possibilité d'étendre les performances GPU et IA grâce à la technologie des chiplets.

On se souviendra ici que pour les SoC R-Car de cinquième génération destinés aux applications hautes performances, Renesas a opté pour le choix d’une technologie d'intégration de type chiplet qui permet d’associer dans un même boîtier-système des circuits intégrés compacts embarquant chacun un sous-ensemble bien défini de fonctionnalités.

On se souviendra ici que pour les SoC R-Car de cinquième génération destinés aux applications hautes performances, Renesas a opté pour le choix d’une technologie d'intégration de type chiplet qui permet d’associer dans un même boîtier-système des circuits intégrés compacts embarquant chacun un sous-ensemble bien défini de fonctionnalités.

A titre d’exemple, en combinant le NPU sur puce de 400 Tops avec un NPU externe via une extension chiplet, il serait possible de multiplier par trois ou quatre, voire plus, les performances de traitement IA d'une puce R-Car X5H.

Pour une intégration sans couture des chiplets, le R-Car X5H prend en charge la technologie d'interconnexion et les API standard UCle (Universal Chiplet Interconnect Express), ce qui, assure Renesas, facilite l'interopérabilité avec d'autres composants dans un système multipuce, même s'il s'agit de puces autres que celles de Renesas. Une approche qui vise à apporter aux ingénieurs automobiles une plus grande flexibilité pour personnaliser leurs conceptions en combinant différentes fonctions, y compris pour les mises à niveau futures sur différentes plateformes de véhicules.

Côté sûreté de fonctionnement, le SoC R-Car X5H s’appuie sur une technologie d’isolation de type matérielle baptisée FFI (Freedom from Interference) qui, selon la société de semi-conducteurs, permet de séparer en toute sécurité les fonctions critiques pour la sûreté (comme le freinage électrique) des fonctions non critiques. Les fonctions jugées critiques peuvent ainsi se voir attribuer leurs propres domaines distincts et redondants, chacun ayant son propre cœur de processeur, sa propre mémoire et ses propres interfaces, ce qui permet d'éviter des défaillances potentiellement catastrophiques du véhicule en cas de faute matérielle ou logicielle issue d'un domaine différent.

Le R-Car X5H est également doté d'une gestion de la qualité de service (QoS) qui détermine les priorités pour les charges de travail et assigne les ressources de traitement en temps réel.

« Les innovations apportées par la plateforme R-Car Gen 5 s'attaquent à relever les défis complexes auxquels l'industrie automobile est confrontée aujourd'hui, indique Vivek Bhan, vice-président et directeur général de la division High Performance Computing de Renesas. Nos clients recherchent des solutions système de bout en bout de classe automobile qui couvrent tous les aspects, de l'optimisation matérielle à la conformité aux normes de sûreté de fonctionnement, en passant par une offre d'architectures flexibles et échelonnables et l'intégration transparente d'outils et de logiciels. Notre famille R-Car Gen 5 répond à ces exigences et nous comptons contribuer à accélérer le développement des véhicules définis par logiciel et les innovations de type Shift-Left (*) pour la prochaine ère des technologies automobiles. »

On rappellera que les puces R-Car Gen 5 de Renesas, dont la feuille de route a été dévoilée il y a tout juste un an, ont vocation à terme, selon le Japonais, à couvrir le plus large éventail des besoins de traitement de l'industrie automobile - des calculateurs zonaux au calculateur centralisé haut de gamme - au service des véhicules divers et variés, de l’entrée de gamme jusqu’aux modèles de luxe. L’architecture matérielle unifiée autour des cœurs Arm doit notamment permettre aux développeurs travaillant sur des puces R-Car Gen 5 de réutiliser les mêmes logiciels, outils et applications, que ce soit sur les nouveaux SoC 64 bits de Renesas ou sur de futurs produits, comme de futurs microcontrôleurs 32 bits dits crossover et microcontrôleurs 32 bits pour l'automobile (voir illustration ci-dessus). A ce titre, la société prévoit d'échantillonner une nouvelle famille de MCU 32 bits avec une sécurité renforcée pour les applications de carrosserie et de châssis au premier trimestre 2025.

Ajoutons enfin que les puces R-Car X5H de Renesas et tous les futurs produits Gen 5 seront pris en charge par la plateforme de développement SCV R-Car Open Access (ROX) récemment lancée (lire notre article).

(*) Les pratiques dites de “décalage vers la gauche” (shift-left practices) consiste à déplacer des activités de test plus tôt dans un processus de développement avec un retour d'informations continu.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée au marché automobile : Embedded-Automotive