La société Mips, positionnée sur le marché des cœurs de processeurs configurables et éco-efficaces (*), annonce la mise à disposition du bloc d’IP RISC-V Mips P8700 à l’ensemble du marché. Le P8700, que Mips avait évoqué dès la mi-2022, est conçu pour répondre aux exigences de transfert intensif à faible latence de données, imposées par les applications automobiles les plus avancées telles que les systèmes d'aide à la conduite et les véhicules autonomes.

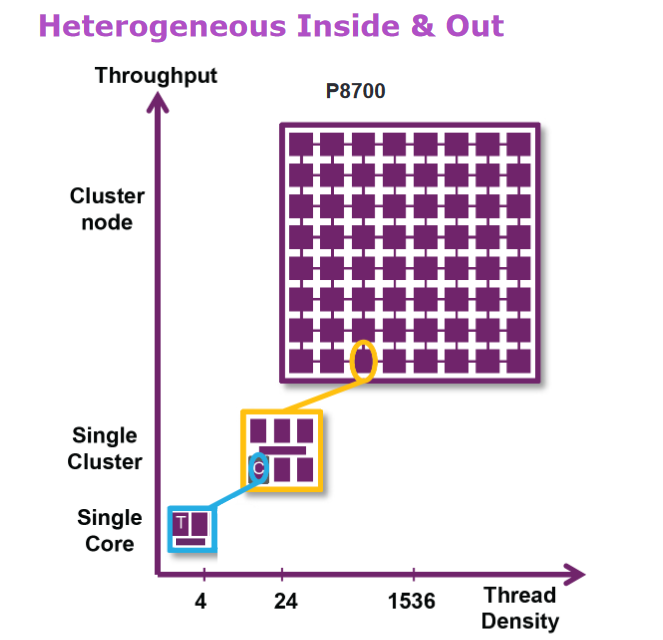

Le modèle multiprocesseur P8700, qui met en œuvre l’architecture RISC-V RV64GC, est présenté comme le premier bloc d’IP RISC-V qui fournit un traitement des instructions dans le désordre (out-of-order) et une échelonnabilité cohérente multithread, multicœur et multicluster, afin d’offrir aux fabricants de puces-systèmes SoC et aux équipementiers un niveau encore jamais atteint de performances RISC-V.

Le modèle multiprocesseur P8700, qui met en œuvre l’architecture RISC-V RV64GC, est présenté comme le premier bloc d’IP RISC-V qui fournit un traitement des instructions dans le désordre (out-of-order) et une échelonnabilité cohérente multithread, multicœur et multicluster, afin d’offrir aux fabricants de puces-systèmes SoC et aux équipementiers un niveau encore jamais atteint de performances RISC-V.

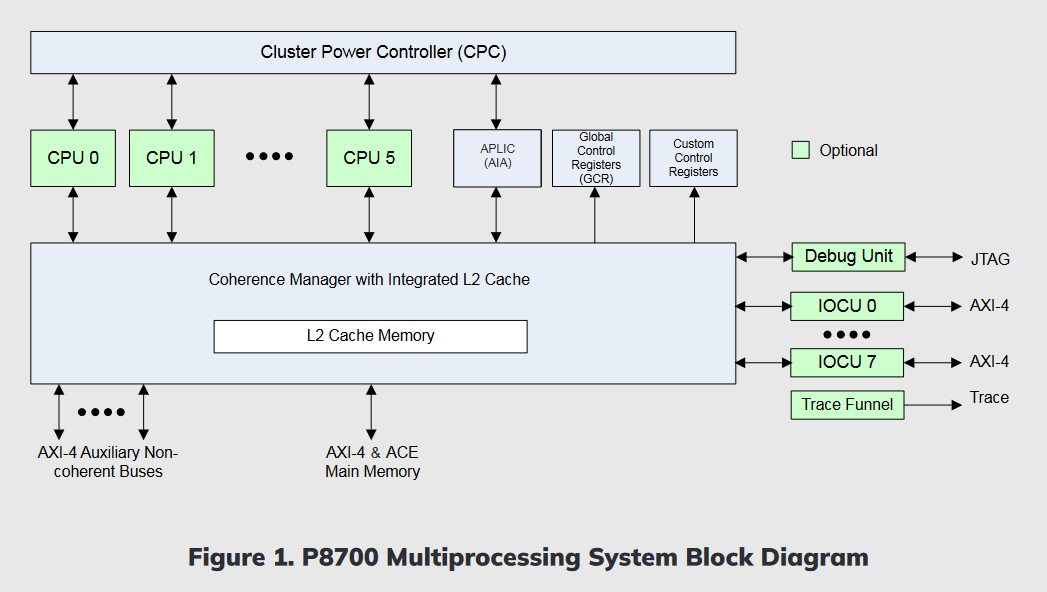

Dans le détail, la structure permet d’associer jusqu'à 6 cœurs P8700 cohérents au sein d’un même cluster, chaque cluster pouvant être connecté directement à des blocs d’accélération (IA notamment).

Selon Mips, les solutions classiques pour systèmes d'aide à la conduite et de conduite autonome reposent sur une approche de force brute qui consiste à intégrer un grand nombre de cœurs à des fréquences d'horloge toujours plus élevées, ce qui permet d'annoncer des performances maximales, alors que celles-ci s’avèrent irréalistes et non réalisables en pratique. A contrario, affirme la société américaine, le P8700, avec son architecture multithread et éco-efficace, permet aux utilisateurs de mettre en œuvre moins de cœurs de processeur et ce dans une enveloppe thermique (TDP) bien inférieure à celle des offres actuelles du marché.

L’architecture choisie par Mips réduirait en outre les goulots d'étranglement système liés à l'inefficacité des transferts des données en fournissant une solution optimisée à faible latence et à consommation réduite, spécifiquement conçue pour les platesformes multicapteurs à niveau élevé d'interruptions. Dans le cadre des systèmes ADAS de niveau L2+ équipés d’une pile logicielle IA autonome, le bloc d’IP P8700 peut également décharger les cœurs de processeur des éléments de traitement de base qui ne peuvent pas être facilement quantifiés dans les modèles d’apprentissage profond et réduits par les fonctions convolutives parcimonieuses, ce qui se traduirait par une utilisation et une efficacité logicielles de la pile IA de plus de 30 %.

« Le marché automobile exige des processeurs capables de traiter une grande quantité de données provenant de plusieurs capteurs en temps réel et d'alimenter les accélérateurs IA pour les traiter de manière efficace, précise Sameer Wasson, le CEO de Mips. Le multithreading Mips et d'autres innovations architecturales adaptées aux besoins des applications automobiles font du P8700 un cœur convaincant pour les tâches de traitement gourmandes en données. Les constructeurs automobiles peuvent ainsi disposer de systèmes de traitement hautes performances qui consomment moins d'énergie et utilisent mieux les accélérateurs IA. » A noter que l’IP multicœur P8700 de Mips a déjà séduit la société Mobileye qui compte l’intégrer dans la plus puissante de ses puces-systèmes conçues spécifiquement pour la conduite automobile automatisée.

Le processeur Mips P8700, conçu pour répondre aux exigences de la norme de sécurité fonctionnelle Asil-B(D) (ISO 26262), est désormais disponible sur le marché au sens large, avec des partenariats clés déjà en place. Les lancements de puces intégrant l’IP de la société américaine sont attendus prochainement.

(*) En 2021, l’américain Wave Computing, qui avait mis la main sur Mips mi-2018, était sorti du régime de protection prévu par le Chapitre 11 de la loi américaine sur les faillites pour reprendre le nom de Mips afin de marquer clairement la réorientation stratégique de la société sur le marché des architectures de processeur Risc (savoir-faire d’origine de Mips avec l'architecture du même nom). La nouvelle entité en avait profité pour dévoiler qu’elle travaillait sur une nouvelle architecture reposant sur le jeu d’instructions open source RISC-V.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée au marché automobile : Embedded-Automotive