[APPLICATION MICROCHIP] Les circuits logiques sur puce et les périphériques de flexibilité améliorent les applications en réduisant la taille du code, en diminuant la consommation énergétique et en améliorant les performances système grâce à l’implantation de composants logiques discrets et/ou à la connexion d’autres périphériques ensemble. Explications de Microchip.

Auteur : Robert Perkel, Ingénieur application, Microchip

Auteur : Robert Perkel, Ingénieur application, Microchip

Les périphériques matériels sur puce sont bien connus pour leur capacité à réduire la consommation énergétique, améliorer les performances, augmenter les capacités des composants et réduire la taille du code. Ces périphériques se déclinent en différents types, des amplificateurs opérationnels aux convertisseurs analogique-numérique améliorés en passant par les modulateurs en largeur d’impulsions et les temporisateurs universels. Les plus puissants de ces périphériques sont ceux qui peuvent mettre en œuvre des circuits logiques discrets ou qui peuvent connecter ensemble d’autres périphériques. Dans ce cadre, les cellules logiques configurables (CLC, Configurable Logic Cell), les circuits logiques personnalisés configurables (CCL, Configurable Custom Logic), le réseau de routage Event System (EVSYS, EVent SYStem) et les périphériques ports pour le routage de signaux peuvent être utilisés pour ajouter de la valeur à un système.

Cellules logiques, circuits logiques, boutons et commutateurs anti-rebond

Les périphériques CLC et CCL sont des tables de conversion programmables (LUT, Look-Up Table), dont chacune est équivalente à une cellule unique d’un FPGA. La fonction logique configurée dans chaque instance du périphérique est définie lors de l’exécution. Les CLC/CCL peuvent fonctionner indépendamment du processeur central, ce qui leur permet de remplacer des puces logiques discrètes dans les systèmes. Un CLC et un CCL se distinguent dans des différences mineures de mise en œuvre : le CLC est spécifique aux microcontrôleurs PIC de Microchip, tandis que le CCL est spécifique aux microcontrôleurs AVR de la société. Mais le fonctionnement de base de chaque périphérique reste identique.

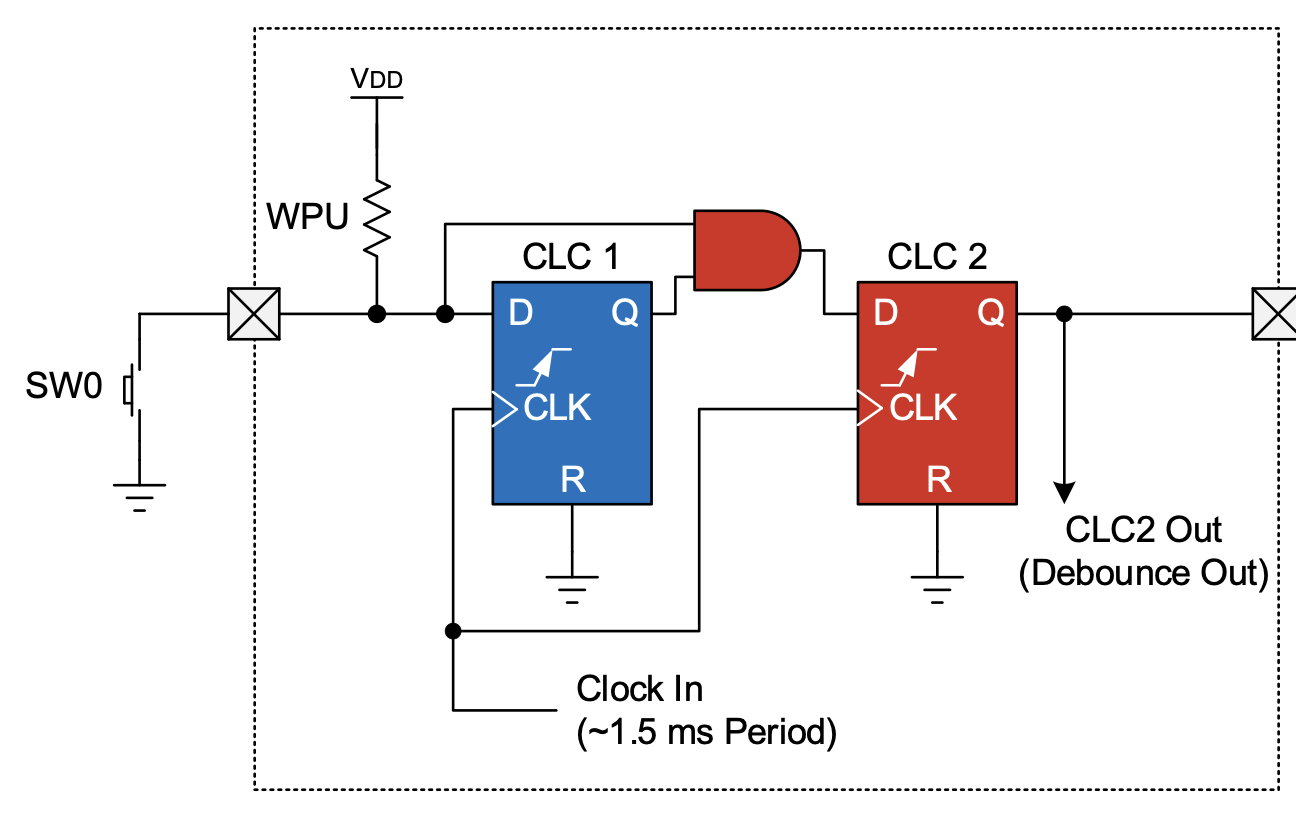

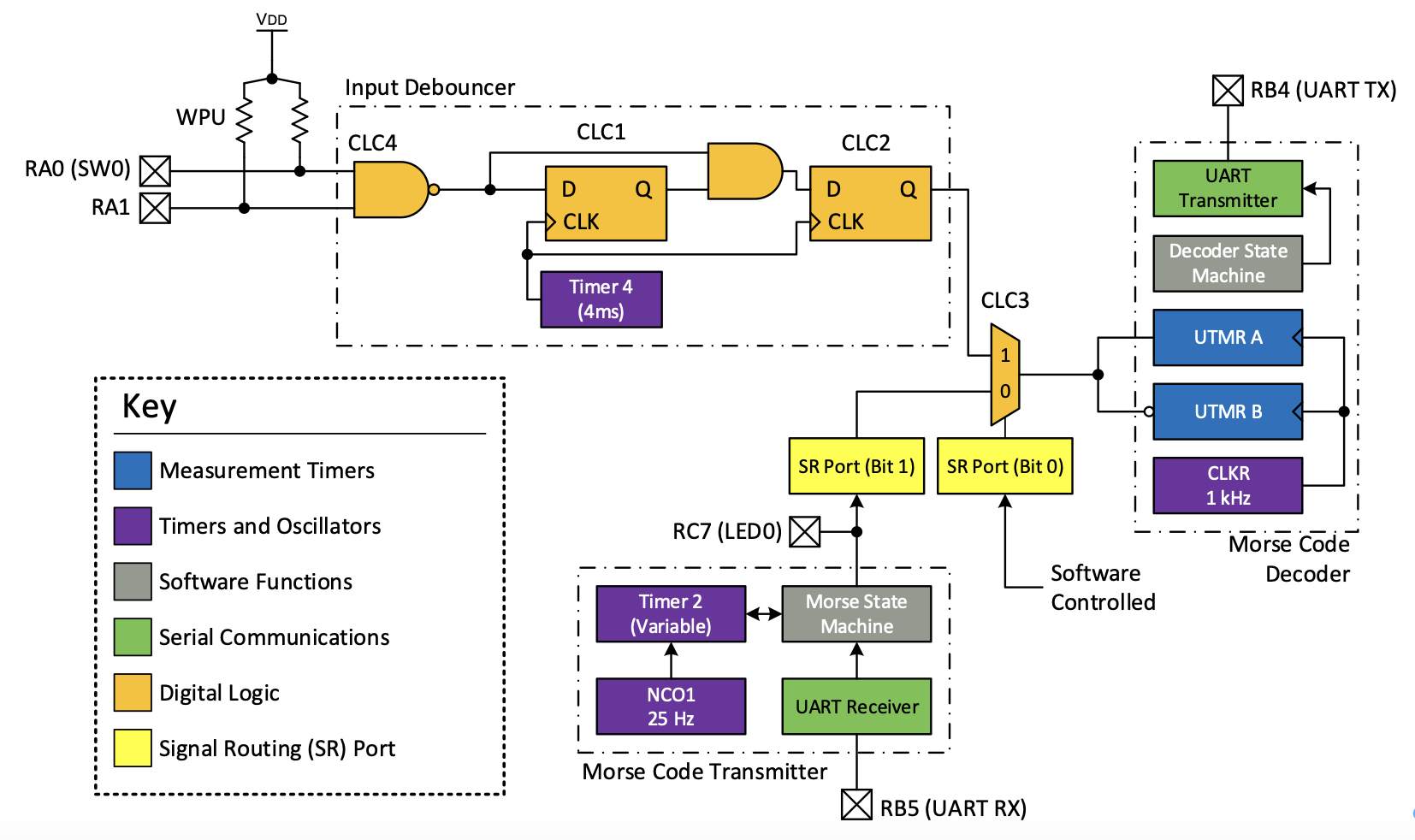

L’un des cas d’utilisation les plus courants des CLC/CCL consiste à mettre en œuvre la fonction d’anti-rebond au niveau matériel associée à un temporisateur/oscillateur. Il existe trois manières de mettre en œuvre l’anti-rebond en utilisant des CLC (*). Parmi ces trois solutions, les deux versions des CLC établissent un équilibre entre l’utilisation des ressources matérielles et les performances. Pour mettre en œuvre l’anti-rebond, l’un des CLC est configuré comme une bascule de type D pour verrouiller la valeur issue du bouton ou du commutateur. Le second CLC ajoute (fonction AND) de façon logique la valeur verrouillée à la première étape à l’entrée directe, puis verrouille la valeur ainsi obtenue. La source d’horloge pour les deux circuits à bascule est une source d’horloge à basse fréquence générée par un temporisateur ou un oscillateur sur le composant. La mise en œuvre est illustrée ci-dessous.

Pour les CCL sur microcontrôleurs AVR, le fonctionnement est encore plus simple. Ces CCL contiennent une option de filtrage qui effectue la même opération de filtrage en deux cycles que celle mise en œuvre sur les CLC. De plus, les CCL peuvent être cadencés à partir d’un oscillateur 1 kHz sur le composant, ce qui est assez lent pour réaliser l’anti-rebond.

Décodage en quadrature

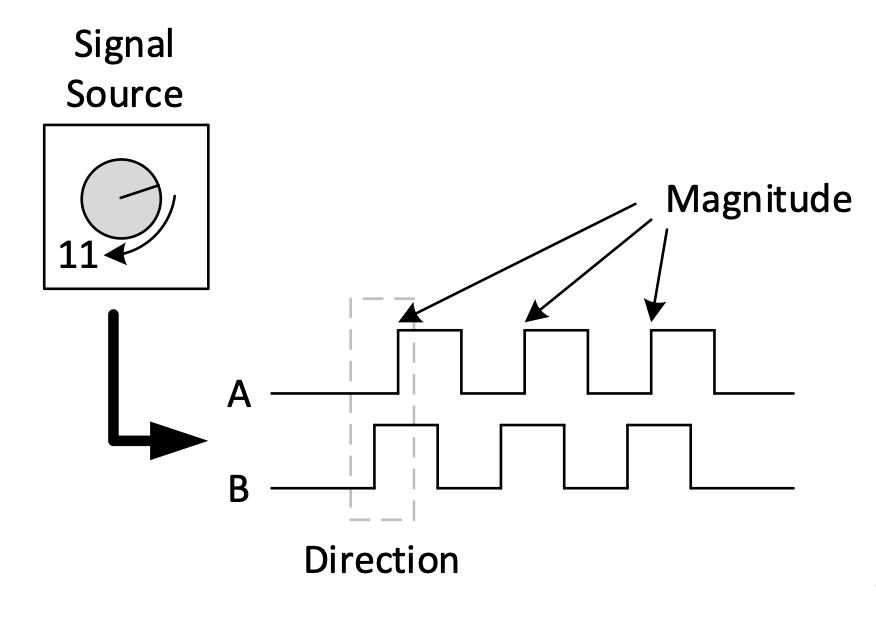

Un autre cas d’utilisation des CLC consiste à réaliser un décodage en quadrature. Les encodeurs en quadratures incrémentaux génèrent deux ondes carrées avec une phase décalée par rapport à l’autre de 90 degrés. La quantité de rotation est déterminée par le nombre de formes d’onde, tandis que la phase de la forme d’onde indique la direction. L’image ci-dessous montre un exemple d’un signal encodé en quadrature.

Pour décoder cela, les CLC convertissent cette forme d’onde en deux sorties, qui représentent les impulsions dans le sens horaire et dans le sens anti-horaire. Deux timers dans le microcontrôleur comptent le nombre d’impulsions reçu. Quand le microcontrôleur a besoin de connaître le changement de position net, quelques calculs simples peuvent être effectués sur les comptages de chaque timer pour déterminer le changement net depuis le dernier relevé.

Pour décoder cela, les CLC convertissent cette forme d’onde en deux sorties, qui représentent les impulsions dans le sens horaire et dans le sens anti-horaire. Deux timers dans le microcontrôleur comptent le nombre d’impulsions reçu. Quand le microcontrôleur a besoin de connaître le changement de position net, quelques calculs simples peuvent être effectués sur les comptages de chaque timer pour déterminer le changement net depuis le dernier relevé.

Réseau de routage, ports SR et sélection du signal sur le composant

Le réseau de routage EVSYS est conçu pour sélectionner un signal de sortie issu d’un autre périphérique et l’acheminer vers un ou plusieurs autres périphériques internes dans le microcontrôleur. Cette interconnectivité peut se produire indépendamment du processeur, ce qui économise de l’énergie lorsque celui-ci est en mode veille ou ralenti, et améliore les performances. EVSYS existe uniquement sur les microcontrôleurs AVR. Sur les microcontrôleurs PIC, il existe un périphérique connu sous le nom de port de routage du signal (SR, Signal Routing Port). Le port SR est une structure qui ressemble à un port d’E/S, mais en interne. Un logiciel peut être utilisé pour le configurer manuellement ou effacer les bits en interne, comme pour un registre d’E/S standard, mais il prend aussi en charge les signaux de sortie du périphérique et la fonctionnalité de registre de décalage.

Le port SR fonctionne également bien avec la sélection PPS (Peripheral Pin Select), que l’on trouve aussi sur les microcontrôleurs PIC. La sélection PPS laisse la flexibilité au développeur d’assigner les E/S en permettant aux signaux d’E/S numériques d’être déplacés vers différentes broches du microcontrôleur. De la même façon, la sélection PPS permet aux périphériques de sélectionner individuellement les « broches » port SR comme entrées.

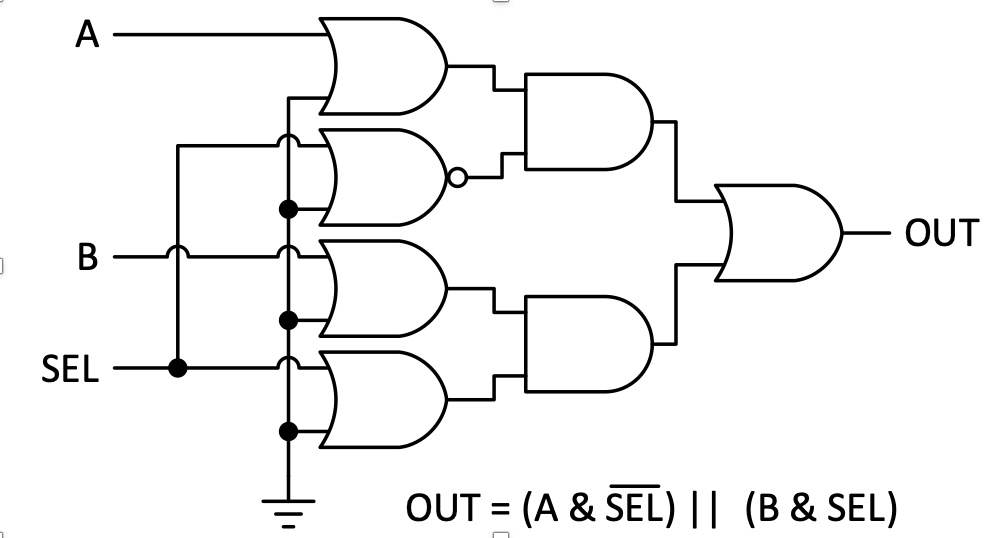

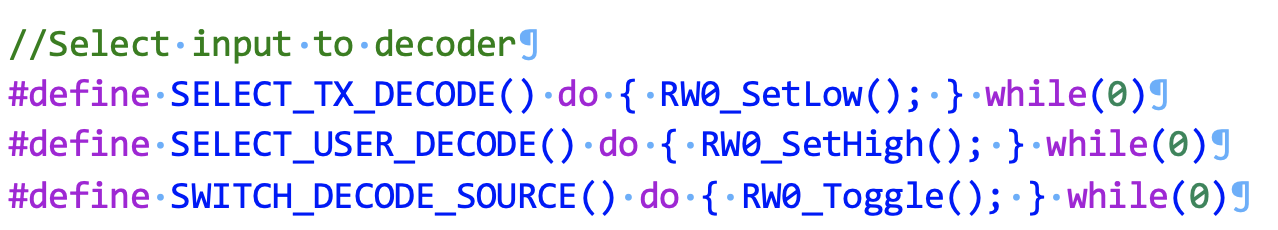

Cela permet de construire des machines d’état avancées et de les commander à l’aide de ces périphériques. L’une des utilisations possibles du port SR et du CLC consiste à mettre en œuvre un multiplexeur de sélection du signal en interne. Il pourra être utilisé pour un auto-test en interne ou pour sélectionner l’un des signaux N à traiter. Pour mettre en œuvre ce multiplexeur, un CLC est utilisé pour créer une multiplexeur 2:1. Il est également possible de créer un multiplexeur 4:1, mais dans ce cas il faut utiliser trois CLC et deux bits du port SR. Pour commander le multiplexeur, un bit issu du port SR est utilisé pour sélectionner la ligne. La mise en œuvre logique est illustrée ci-dessous.

L’un des avantages de cette implémentation par rapport à la sélection PPS est sa vitesse et sa flexibilité. La sélection PPS peut être verrouillée pour prévenir les changements inopinés lors de l’exécution. De plus, un bit de configuration peut être défini pour s’assurer que la sélection PPS ne peut être déverrouillée qu’une seule fois. À la place, la configuration du multiplexeur CLC permet au programme de changer les entrées sans passer par une séquence de déverrouillage à chaque fois. Ce cas d’utilisation est utilisé dans la démonstration du code Morse pour la famille de PIC18F56Q71 de Microchip. La démonstration crée un simple émetteur-récepteur de code Morse. Le multiplexeur est utilisé pour opérer la sélection entre la sortie de l’émetteur et un signal d’entrée externe pour la réception (**).

À l’intérieur du programme, des macros de définition/effacement/bascule d’un seul bit pour les broches du port SR sont définies pour plus de lisibilité.

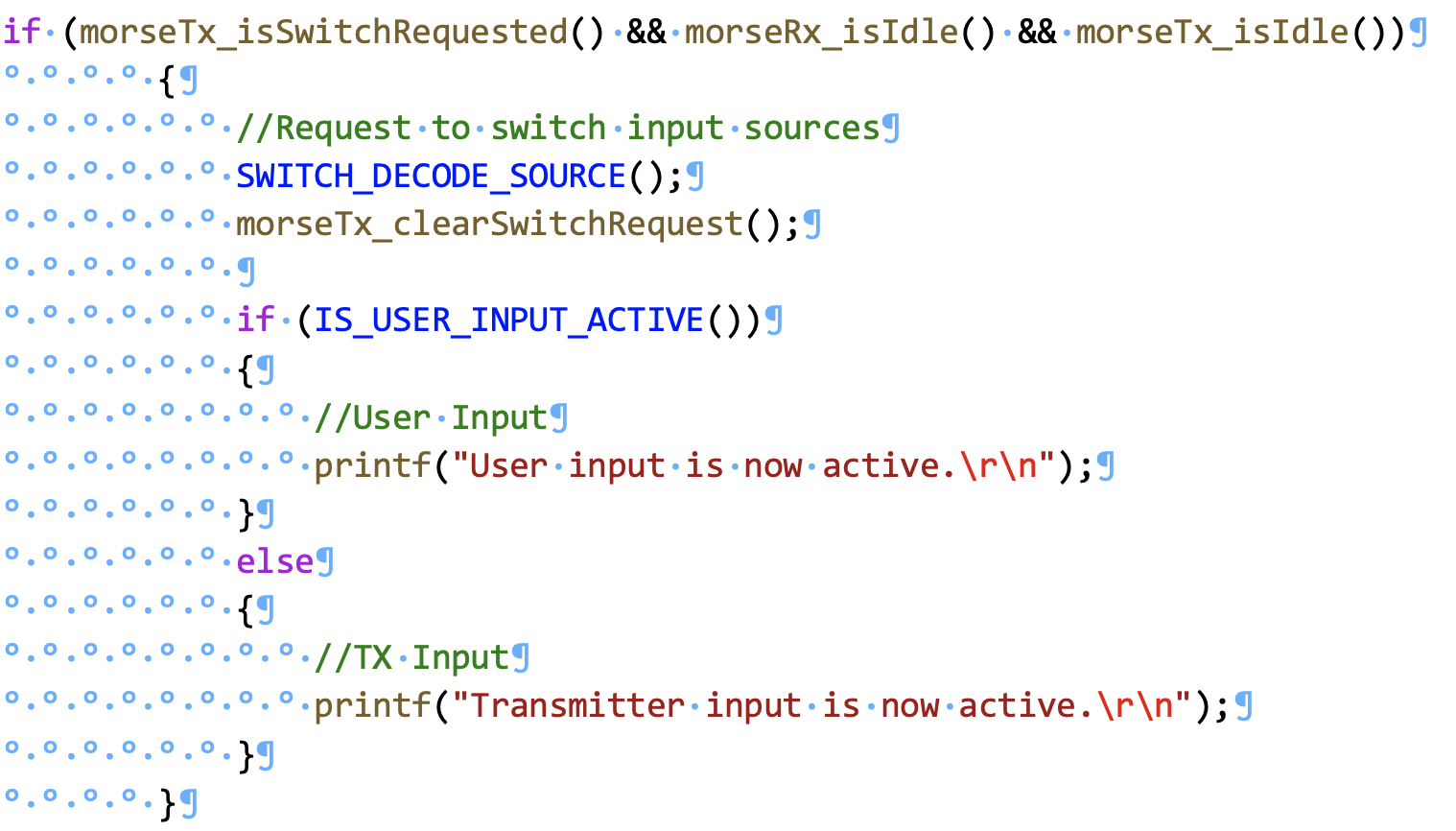

L’extrait de code ci-dessous a pour rôle de nettoyer la commutation entre les sources d’entrée. Lorsque l’émetteur et le récepteur sont au ralenti, et que l’utilisateur a envoyé un # au terminal, il commute les sources d’entrée.

Calcul de parité au niveau matériel

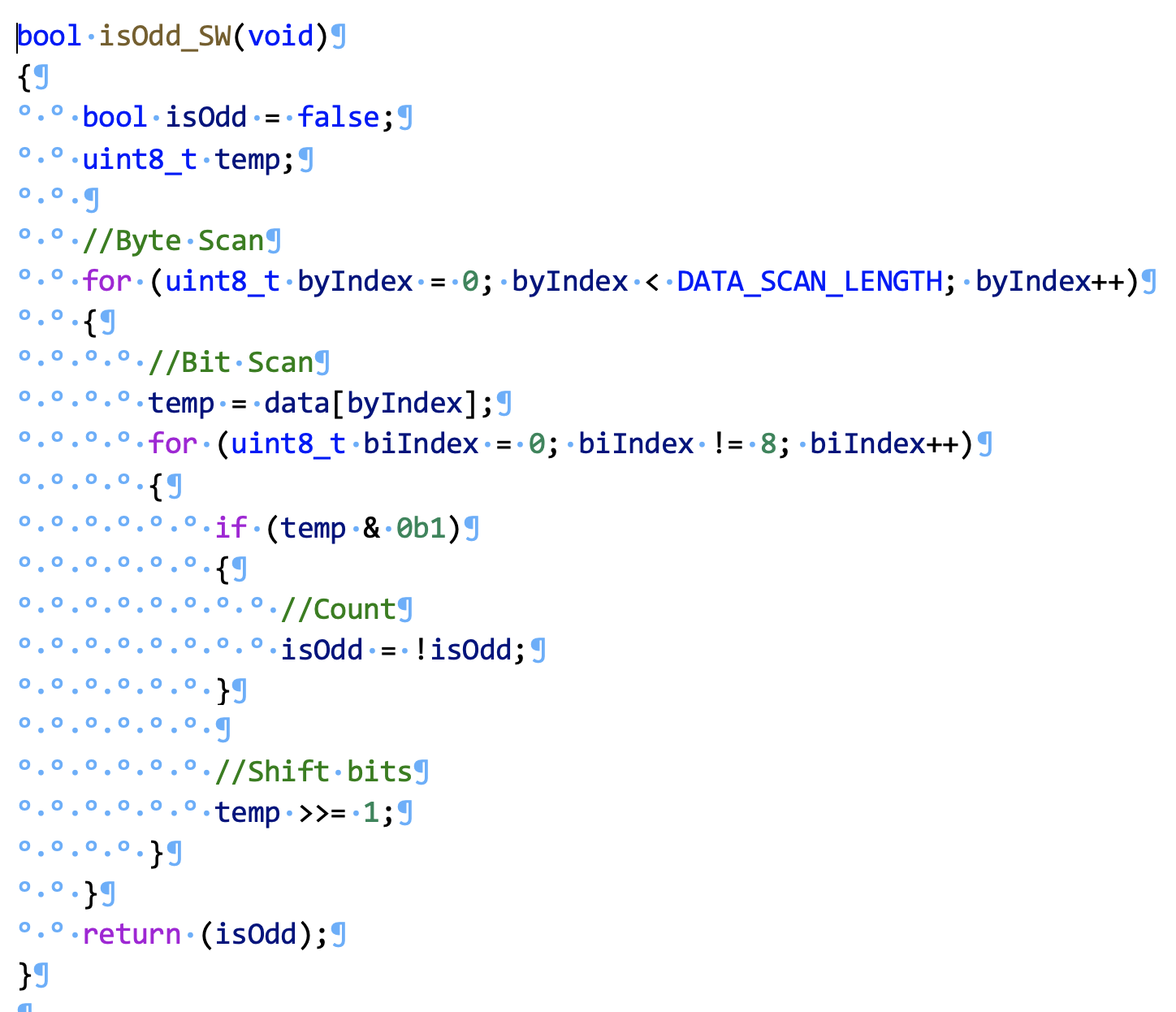

Dans certains cas, il est nécessaire de générer un bit de parité pour la transmission de données ou la communication. Le calcul de parité avec un logiciel est trivial, mais plus lent à exécuter qu’au niveau matériel. Vous trouverez ci-dessous un exemple de fonction simple (dans lequel le pattern de test évalué est stocké localement pour ces exemples simples).

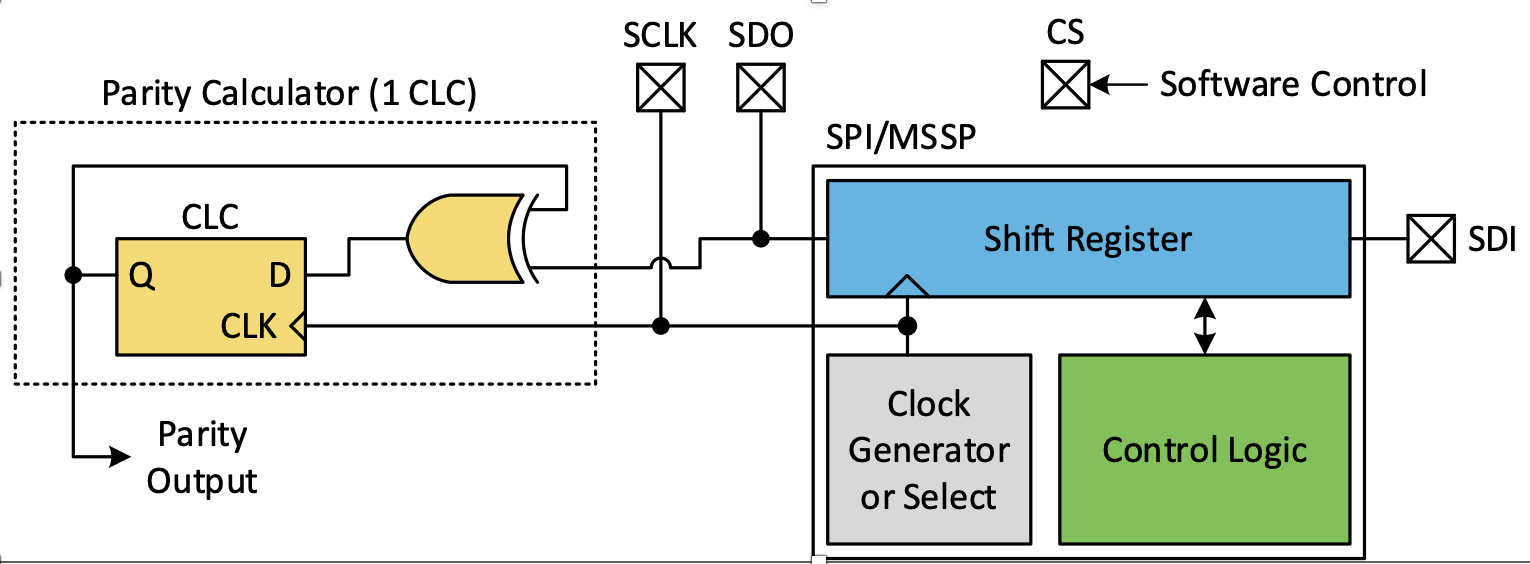

Pour accélérer le calcul, on peut utiliser un périphérique SPI avec une cellule CLC pour créer un calculateur de parité matériel. Le SPI contient le registre à décalage série pour envoyer et recevoir les données. La sortie du SPI (le registre de décalage) peut être envoyée vers un CLC pour créer un calculateur de parité qui fonctionne à une vitesse substantiellement plus rapide que la version logicielle.

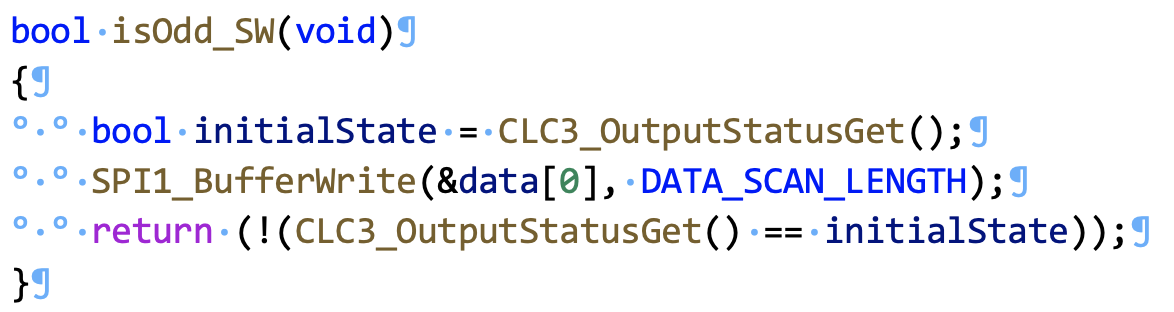

Cette mise en œuvre peut également réutiliser un périphérique SPI existant, ce qui diminuera encore les coûts de mise en œuvre. En effet, normalement, la ligne Chip Select (CS) doit être déclarée pour communiquer avec d’autres composants SPI. Cependant, si elle n’est pas déclarée, alors la communication est ignorée. Pour réaliser la version accélérée au niveau matériel, il faut capturer d’abord la valeur de courant verrouillée dans le CLC. Puis il faut envoyer les données pour qu’elles soient calculées selon la parité avec le CS non déclaré. Ensuite, il faut relever la nouvelle valeur verrouillée dans le CLC. Si la nouvelle valeur est égale à la valeur précédente, cela signifie qu’un nombre pair de 1 à été compté. Si la nouvelle valeur est différente, cela signifie qu’il y a un nombre impair de 1. Le logiciel servant à calculer une parité impaire est montré ci-après.

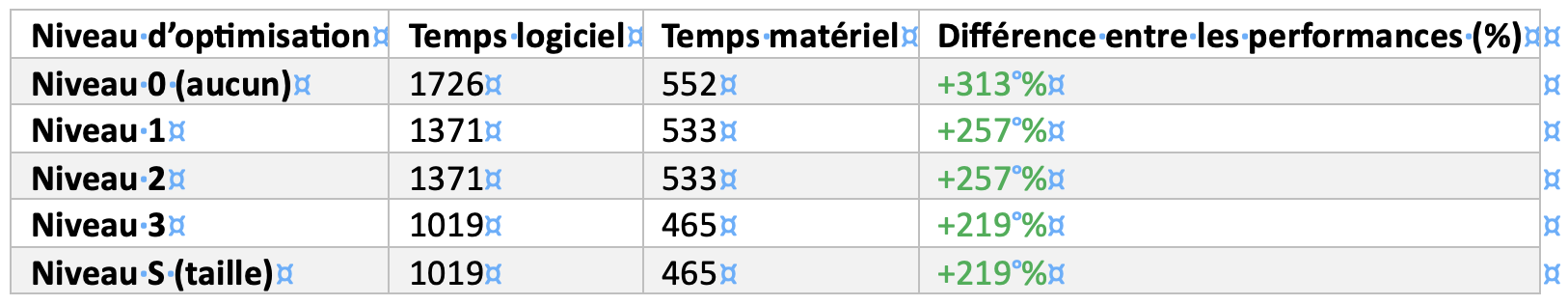

Afin de prouver la vitesse supérieure de la solution matérielle, un petit programme de démonstration a été créé sur les microcontrôleurs de la famille PIC16F18146 de Microchip. L’un des temporisateurs internes, le Timer 1, est utilisé pour compter le nombre de cycles d’horloge (FOSC/4) nécessaire pour exécuter les calculs de parité aux niveaux matériel et logiciel. Les résultats sont imprimés par un terminal série à des fins d’analyse.

On peut retrouver ci-dessous une copie des résultats obtenus pour différents niveaux d’optimisation du compilateur.

Différences de performances entre les mises en œuvre logicielle et matérielle, séquence de 10 octets

L’amélioration des performances que l’on peut observer dans le présent exemple dépend de la vitesse de l’horloge du microcontrôleur et de celle du périphérique SPI. Le code source de ce programme est disponible sur GitHub. Les périphériques matériels sont des caractéristiques importantes sur les systèmes embarqués.

Quand ils sont utilisés, les microcontrôleurs deviennent puissants, efficaces et dotés de grandes capacités. Les périphériques logiques et de flexibilité sont des outils particulièrement puissants pour la gestion de tâches simples comme l’anti-rebond ou le décodage en quadrature. L’utilisation créative des périphériques matériels améliore les systèmes et repousse les limites des possibilités des microcontrôleurs.

(*) Trois manières d’utiliser les CLC/CCL sont décrites dans la note d’application 2805 (AN2805). Le code source pour ces trois versions est disponible sur GitHub.

(**) On peut voir ici la démonstration du code Morse pour la famille des circuits PIC18F56Q71 de Microchip.