Spécialiste des IP d’instrumentation, de débogage et d’analyse de trace pour les designs de puces-systèmes, le britannique UltraSoC a ajouté à son infrastructure de surveillance et d’analyse intégrée pour conceptions de SoC, une fonction de suivi de l’activité de la puce précise au niveau cycle (cycle accurate).... Cette traçabilité précise des cycles est importante dans les applications qui nécessitent la gestion du temps réel critique et des performances associées, là où les ingénieurs doivent optimiser le fonctionnement de leurs codes matériel et logiciel jusqu'au niveau du cycle d'horloge - la plus petite unité temporelle reconnue par un processeur, un processeur graphique, un DSP ou un bloc d’accélération.

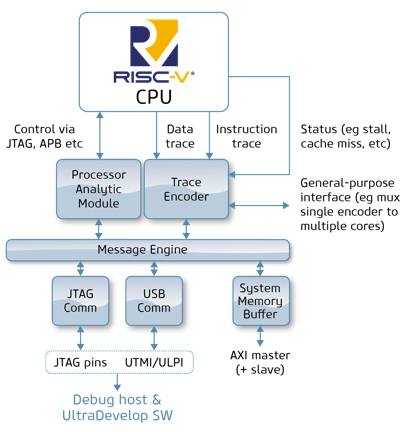

Ce traçage précis des activités d’un circuit sera disponible dans un premier temps au sein de la solution d’analyse de trace du processeur RISC-V d’UltraSoC pour des applications de type gestion de disques durs à semi-conducteurs SSD ou de serveur embarqué temps réel.

La technologie d’analyse et de surveillance d’UltraSoC étant directement intégrée au niveau matériel sur la puce, elle peut capturer les événements au sein d’un SoC, dans une fenêtre de l’ordre de quelques nanosecondes. L'accès à ces informations de traçage précises au niveau cycle signifie que les concepteurs sont en mesure de savoir exactement combien de cycles leur code prend pour s'exécuter, s'il y a des arrêts et des dépendances et quelle est la durée de ceux-ci. Les logiciels ne se comportent pas en effet toujours comme prévu en raison de l’interaction entre logiciels, périphériques, événements temps réel issus d’autres cœurs, etc. Avec comme résultat un comportement en temps réel affecté. La trace du processeur est donc une exigence clé pour les développeurs système car elle permet de visualiser le comportement d'un programme en détail, instruction par instruction. Quant à la trace précise au niveau cycle, elle permet, au-delà, de savoir à quel instant chaque ligne de code a été exécutée. Forts de ces informations, les concepteurs de systèmes critiques peuvent alors procéder à de nouvelles optimisations.

La technologie d’analyse et de surveillance d’UltraSoC étant directement intégrée au niveau matériel sur la puce, elle peut capturer les événements au sein d’un SoC, dans une fenêtre de l’ordre de quelques nanosecondes. L'accès à ces informations de traçage précises au niveau cycle signifie que les concepteurs sont en mesure de savoir exactement combien de cycles leur code prend pour s'exécuter, s'il y a des arrêts et des dépendances et quelle est la durée de ceux-ci. Les logiciels ne se comportent pas en effet toujours comme prévu en raison de l’interaction entre logiciels, périphériques, événements temps réel issus d’autres cœurs, etc. Avec comme résultat un comportement en temps réel affecté. La trace du processeur est donc une exigence clé pour les développeurs système car elle permet de visualiser le comportement d'un programme en détail, instruction par instruction. Quant à la trace précise au niveau cycle, elle permet, au-delà, de savoir à quel instant chaque ligne de code a été exécutée. Forts de ces informations, les concepteurs de systèmes critiques peuvent alors procéder à de nouvelles optimisations.

Ces capacités de traçage au niveau cycle renforcent le savoir-faire d’UltraSoC dans le domaine du développement et du débogage de puces architecturées autour d’un cœur de processeur RISC-V. Rappelons que dès le début 2018, la société a mis à disposition des développeurs un bloc de propriété intellectuelle (IP) conçu spécifiquement pour l’analyse de trace du processeur RISC-V, afin de surveiller l’exécution des programmes en temps réel. La technologie mise en œuvre consiste à coder l'exécution des instructions et, éventuellement, les accès à la mémoire de données afin de générer un format de trace fortement compressé. Un logiciel externe récupére ensuite ces données et les utilise pour reconstruire un flux d'exécution du programme.

Des partenariats avec Andes et Wave Computing

Le codeur de trace RISC-V d'UltraSoC a été développé pour être conforme aux spécifications ouvertes du RISC-V, tout en offrant des fonctionnalités de haut niveau - traçage des données et des instructions, gamme de compteurs et de minuteries et fonctions de profilage rapide - le différenciant, selon la société, des solutions purement open source.

Décidément très actif sur le front RISC-V, UltraSoC a aussi annoncé qu’il allait coopérer avec Andes Technology, fournisseur asiatique de cœurs de processeurs 32 bits et 64 bits RISC-V, qui va intégrer la technologie d’UltraSoC dans son offre de processeurs RISC-V AndesCore.

Dans le même temps, la technologie d’UltraSoC a aussi été choisie par Wave Computing pour tester sa plate-forme évolutive TritonAI 64 pour les SoC intelligents. L’utilisation de la plate-forme UltraSoC par Wave Computing servira notamment de modèle de référence pour les clients qui doivent valider et déboguer des modèles de puces-systèmes à blocs d'IP hétérogènes. Cette plate-forme TritonAI 64 contient trois moteurs de traitement - WaveFlow, WaveTensor et WaveRT - tous basés sur un cœur de processeur Mips32.

Une levée de fonds de 5 millions de livres

Enfin, pour être complet, signalons qu'UltraSoC vient de sécuriser un investissement de 5 millions de livres sterling. Dans ce tour de table, eCapital, une société de capital-risque axée sur la cybersécurité, et Seraphim Capital, un investisseur spécialisé dans l'écosystème spatial, ont rejoint les investisseurs existants tels qu'Octopus Ventures, Oxford Capital, Techgate et le business angel Guillaume d'Eyssautier. Dans le cadre de son développement, UltraSoC recrutera des ingénieurs hardware au sein de son siège situé à Cambridge, au Royaume-Uni, et dans un centre de conception à Bristol, également au Royaume-Uni. La société prévoit également d'ouvrir un centre d'ingénierie à Varsovie, en Pologne, afin de développer ses technologies de traitement de données et d'apprentissage automatique.

-dissolve-basic-fr.jpg)