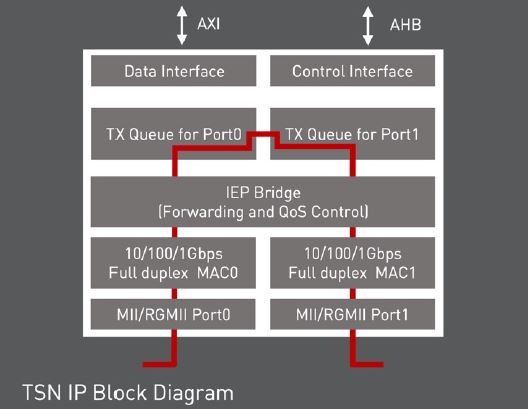

Société issue de la combinaison des activités de développement de puces-systèmes SoC de Fujitsu et de Panasonic, Socionext a développé un bloc d’IP TSN (Time Sensitive Networking) destiné à une mise en œuvre dans des FPGA ou des Asic. ...On rappellera que les mécanismes TSN, spécifiés par le groupe de travail TSN du comité IEEE 802.1, visent à assurer la convergence des technologies de communication Ethernet offrant transfert déterministe de données à haut débit et synchronisation temporelle à haute précision. Avec TSN, les données de contrôle/commande à faible latence et le trafic Ethernet standard peuvent donc cohabiter sur le même support physique.

Parmi les caractéristiques fournies par ce bloc d’IP, on citera la prise en charge de deux ports pour la connexion d’équipements industriels dans une topologie en guirlande, un fonctionnement à 1 Gbit/s, une latence réduite à moins de 400 ns et une gigue minimale (moins de 0,1 µs) (voir illustration ci-contre).

Les applications industrielles ciblées vont des contrôleurs de mouvement aux entrées/sorties distantes, sachant que la technologie TSN a aussi vocation à faire converger les réseaux informatiques (IT) et opérationnels (OT) dans le cadre de l’usine « intelligente ».

-dissolve-basic-fr.jpg)