Fondée par les créateurs de l’architecture de processeur open source RISC-V à l’université de Californie à Berkeley, la société SiFive, en annonçant la disponibilité immédiate de sa famille d’IP Coreplex, estime aujourd’hui considérablement simplifier l’accès aux cœurs de processeur RISC-V. ...La start-up, qui vient de boucler un tour de table de 8,5 millions de dollars (et porter les fonds levés depuis sa création à 13,5 M$) et qui se targue d’être devenu le leader de facto de l’écosystème RISC-V, estime que les concepteurs peuvent désormais disposer en quelques minutes du code RTL de ses blocs d’IP Coreplex E31 et E51.

Si l’on en croit la firme américaine, le site de SiFive fournit toutes les informations qui permettent à un utilisateur potentiel d’étudier en détail les IP de la société, dont des fiches produit détaillées, des spécifications et des notes d’application, toutes accessibles sans signer d’accords de confidentialité. En un clic, le concepteur pourrait alors disposer instantanément des modèles de bitstream à charger sur un FPGA pour tester le logiciel, le SDK et les outils. Un code RTL d’évaluation pleinement opérationnel et synthétisable serait également disponible instantanément. Enfin un contrat simplifié de sept pages avec des formules tarifaires claires permettrait de licencier l’IP pour un usage commercial.

Accessible sous licence open source BSD et sans paiement de redevances à la différence des approches de sociétés comme ARM Mips, RISC-V, rappelons-le, définit un jeu d’instructions basé sur les principes des architectures matérielles de processeurs Risc (Reduced Instruction Set Computer). Selon ses promoteurs, ses caractéristiques, doublées de ses capacités d’extension (avec des instructions d’unité de calcul en virgule flottante par exemple), le rendent adapté aussi bien aux serveurs dans le cloud qu’aux terminaux mobiles ou aux systèmes embarqués les plus contraints. (Pour plus de détails, lire nos articles Une alternative open source commence à briller au firmament des architectures de processeurs et L’architecture de processeurs open source RISC-V fait son show sur Embedded World.) Ajoutons que SiFive proposait déjà un SoC RISC-V (FE310) calibré pour les applications embarquées, IoT et portées sur soi, ainsi qu’une carte de développement ad hoc bas coût (HiFive1).

Accessible sous licence open source BSD et sans paiement de redevances à la différence des approches de sociétés comme ARM Mips, RISC-V, rappelons-le, définit un jeu d’instructions basé sur les principes des architectures matérielles de processeurs Risc (Reduced Instruction Set Computer). Selon ses promoteurs, ses caractéristiques, doublées de ses capacités d’extension (avec des instructions d’unité de calcul en virgule flottante par exemple), le rendent adapté aussi bien aux serveurs dans le cloud qu’aux terminaux mobiles ou aux systèmes embarqués les plus contraints. (Pour plus de détails, lire nos articles Une alternative open source commence à briller au firmament des architectures de processeurs et L’architecture de processeurs open source RISC-V fait son show sur Embedded World.) Ajoutons que SiFive proposait déjà un SoC RISC-V (FE310) calibré pour les applications embarquées, IoT et portées sur soi, ainsi qu’une carte de développement ad hoc bas coût (HiFive1).

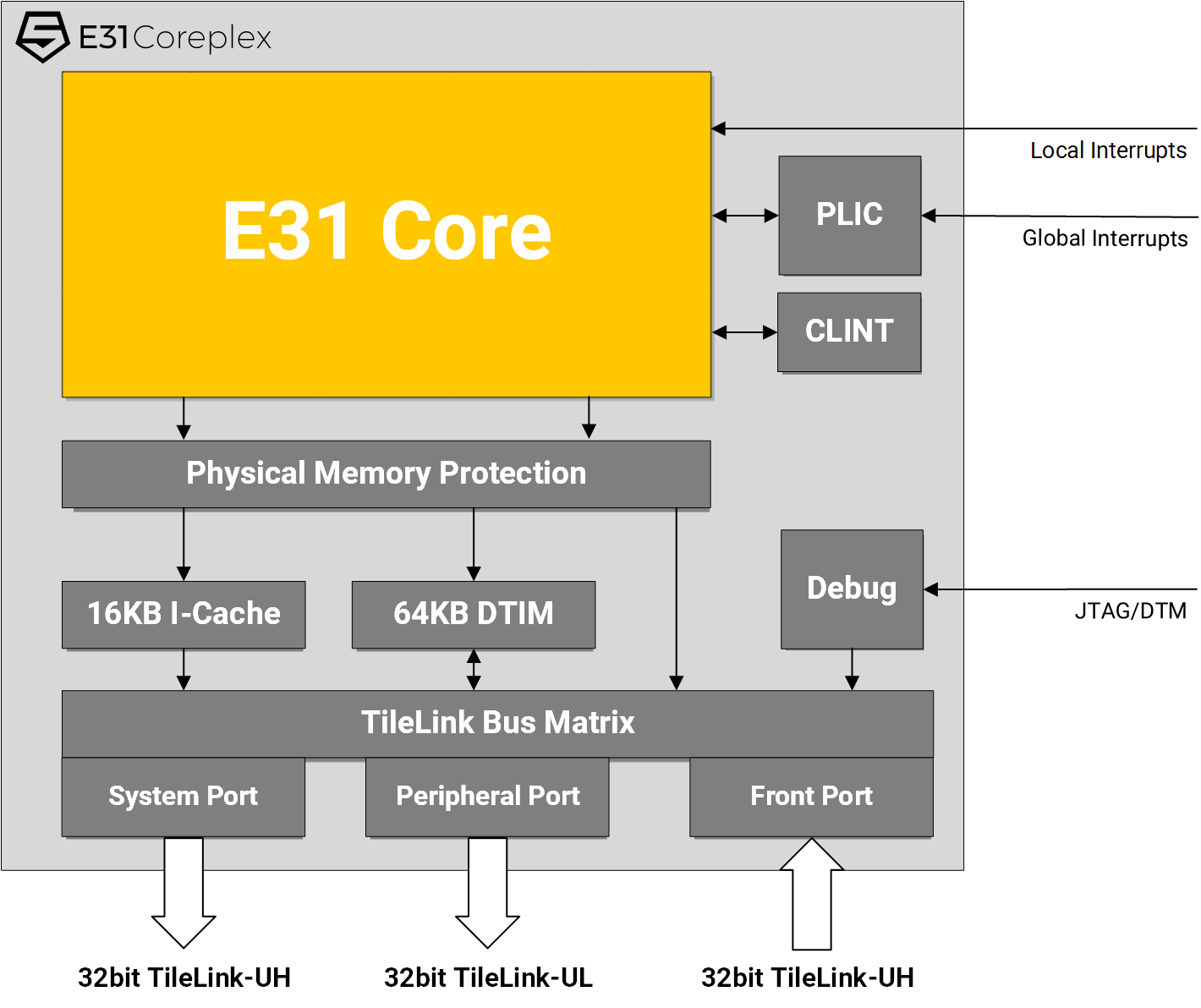

Dans le détail, l’IP Coreplex E31 est conçue pour les applications embarquées 32 bits hautes performances et basse consommation (edge computing, Internet des objets, dispositifs électroniques portés sur soi). De son côté, l’IP Coreplex E51 est un cœur 64 bits qui se positionne idéalement comme cœur de contrôle hôte ou système dans un SoC 64 bits, sa faible empreinte silicium et son éco-efficacité le distinguant des gros processeurs 64 bits traditionnellement utilisés aujourd’hui, assure SiFive.

-fr.jpg)